**BUFFER REGISTERS**

8200

N,F,Q PACKAGES

8201 8202

# DIGITAL 8000 SERIES TTL/MSI

8203

#### DESCRIPTION

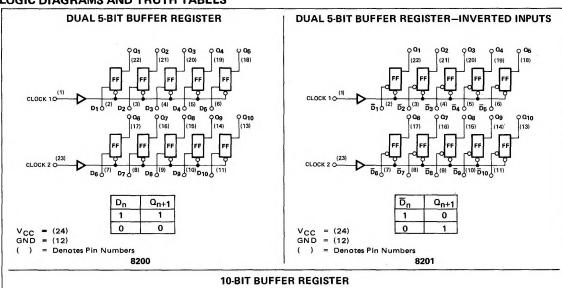

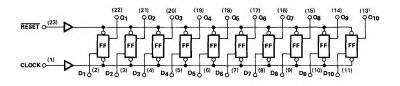

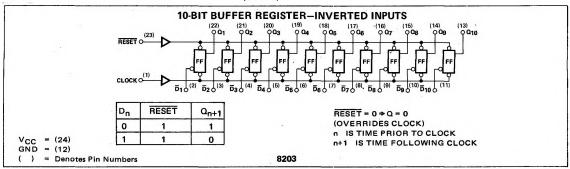

The 8200/8201/8202/8203 MSI Buffer Registers are arrays of ten clocked "D" flip-flops especially suited for parallel-in parallel-out register applications. They are also suitable for general purpose applications as parallel-in serial-out, serial-in parallel-out registers.

The flip-flops are arranged as dual 5 arrays, (8200 & 8201) and single 10 arrays with reset, (8202 & 8203). The true output of each bit is made available to the user.

The 8200 and 8202 feature true "D" inputs. The logic state presented at these "D" inputs will appear at the Q outputs after a negative transition of the clock.

The 8201 and 8203 feature complementing "D" inputs ("\overline{D}"). The logic state presented at these "\overline{D}" inputs will invert and appear at the Q outputs after a negative going transition of the clock. This complementing input feature ("\overline{D}") permits the use of standard AND-OR-INVERT gates to achieve the AND-OR function without additional gate delays.

## **LOGIC DIAGRAMS AND TRUTH TABLES**

| Ì | Dn | RESET | Q <sub>n+1</sub> |  |  |  |

|---|----|-------|------------------|--|--|--|

|   | 1_ | 1     | 1                |  |  |  |

|   | 0  | 1     | 0                |  |  |  |

|   |    |       |                  |  |  |  |

V<sub>CC</sub> = (24)

GND = (12) ( ) = Denotes Pin Numbers RESET = 0 → Q = 0 (OVERRIDES CLOCK) n IS TIME PRIOR TO CLOCK n+1 IS TIME FOLLOWING CLOCK

8202

### LOGIC DIAGRAMS AND TRUTH TABLES (Cont'd)

## ELECTRICAL CHARACTERISTICS (Over Recommended Operating Temperature And Voltage)

| CHARACTERISTICS                      |      | LIMITS   |         |              | TEST CONDITIONS                |                                |       |                       |         |       |

|--------------------------------------|------|----------|---------|--------------|--------------------------------|--------------------------------|-------|-----------------------|---------|-------|

|                                      | MIN, | TYP,     | MAX.    | UNITS        | D <sub>n</sub><br>8200<br>8202 | D <sub>n</sub><br>8201<br>8203 | CLOCK | RESET<br>8202<br>8203 | OUTPUTS | NOTES |

| "1" Output Voltage                   | 2.6  | 3.5      |         | <sub>v</sub> | 2.0V                           | 0.8∨                           | Pulse |                       | – 800μA | 6     |

| "0" Output Voltage                   |      |          | 0.4     | v            | 0.8V                           | 2.0V                           | Pulse |                       | 9.6mA   | 7     |

| "0" Input Current                    |      |          |         |              |                                |                                |       |                       |         |       |

| D <sub>n</sub> (8200, 8202)          | -0.1 |          | -1.6    | mA           | 0.4V                           |                                | J     |                       | ,       |       |

| ნე(8201, 8203)                       | -0.1 | 1        | -1.6    | mA           |                                | 0.4V                           | ľ     |                       |         | ľ     |

| Clock                                | -0.1 |          | -1.6    | mA           |                                |                                | 0.4V  |                       |         |       |

| Reset (8202, 8203) '1" Input Current | -0.1 |          | -1.6    | mA           |                                |                                |       | 0.4V                  |         |       |

| D <sub>n</sub> (8200, 8202)          | Ì    |          | 40      | μA           | 4.5V                           |                                |       |                       |         |       |

| Dn (8201, 8203)                      | [    |          | 40      | μΑ           |                                | 4.5V                           |       |                       |         |       |

| Clock                                | ŀ    |          | 40      | μА           |                                |                                | 4.5V  |                       |         | l     |

| Reset (8202, 8203)                   |      |          | 40      | μΑ           |                                |                                |       | 4.5V                  |         | 1     |

| Input Voltage Rating                 |      |          | 1       |              |                                |                                |       |                       |         |       |

| (All inputs)                         | 5.5  |          |         | v            | 10mA                           | 10mA                           | 10mA  | 10mA                  |         |       |

| Power/Current Consumption            |      | 409/77.7 | 580/110 | mW/mA        | 0V                             | 0V                             | ov    | 100                   |         | 11,13 |

# $T_A = 25^{\circ}C$ and $V_{CC} = 5.0V$

|                              | LIMITS |                |     |       | ###################################### |       |

|------------------------------|--------|----------------|-----|-------|----------------------------------------|-------|

| CHARACTERISTICS              | MIN.   | MIN. TYP, MAX. |     | UNITS | TEST CONDITIONS                        | NOTES |

| Propagation Delay            | :      |                |     |       |                                        |       |

| ton Clock to Q               |        | 30             | 45  | ns    |                                        | 8     |

| toff Clock to Q              |        | 25             | 40  | ns    |                                        | 8     |

| ton Reset to Q               |        | 30             | 45  | ns    |                                        | 8     |

| Set Up Time                  |        | 6              | 15  | ns    |                                        | 10    |

| Hold Time                    |        | 0              | ` 5 | ns    |                                        | 12    |

| Minimum Clock Pulse Width    |        | 12             | 17  | ns    |                                        | [     |

| Transfer Rate                | 15     | 35             |     | MHz   |                                        | 8     |

| Output Short Circuit Current | -20    |                | -70 | mA    |                                        | 9, 13 |

#### NOTES:

- All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are tied to V<sub>CC</sub>.

- All measurements are taken with ground pin tied to zero volts.

- Positive current is defined as into the terminal referenced.

- Positive logic definition:

- "UP" Level = "1", "DOWN" Level = "0 ".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- Output source current is supplied through a resistor to 6. ground.

- Output sink current is supplied through a resistor to V<sub>CC</sub>.

- Refer to AC Test Figure. R.

- 9. Not more than one output should be shorted at a time.

- Set Up Time defined as data presence before clock. 10.

- 11. Outputs are in the low state for this test.

- Hold time defined as data presence after clock. 12.

- 13. V<sub>CC</sub> = 5.25 volts.

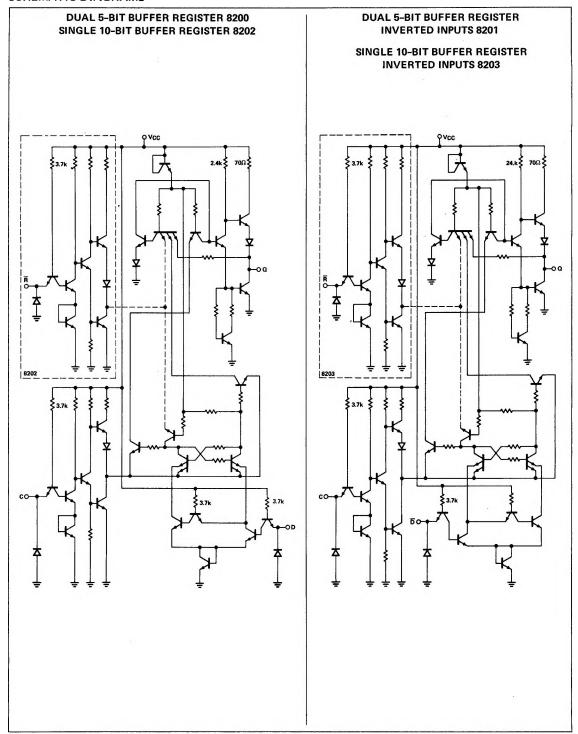

## **SCHEMATIC DIAGRAMS**

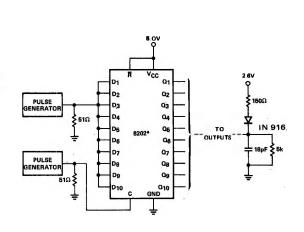

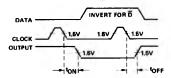

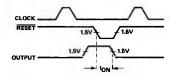

### **AC TEST FIGURES AND WAVEFORMS**

INPUT PULSE: Date = P.R.R. = 7.5 MHz Clock = P.R.R. = 15 MHz PW = 17 ns (at 50% point)  $t_r = t_f = 5$  ns Mex. Amplitude = 2.6V.

\*Refer to the Pin-Outs for the 8200/01/03 AC Testing.

tpd FROM CLOCK TO Q

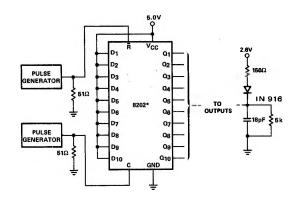

# ton FROM RESET TO Q

INPUT PULSE: Amplitude = 2.6V Clock: P.R.R. = 5 MHz Reset: P.R.R. = 5 MHz PW = 30 ns (at 50% point) t<sub>r</sub> = t<sub>f</sub> = 5 ns

\*Refer to the Pin-Outs for the 8200/01/02/03 AC Testing.

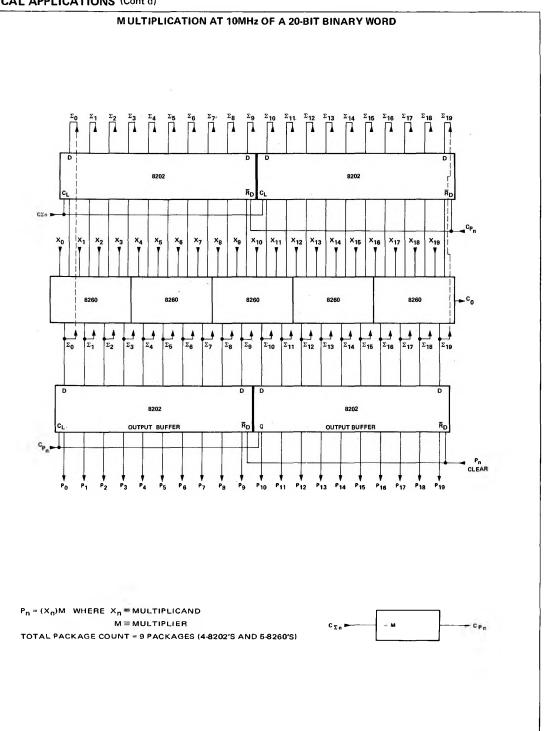

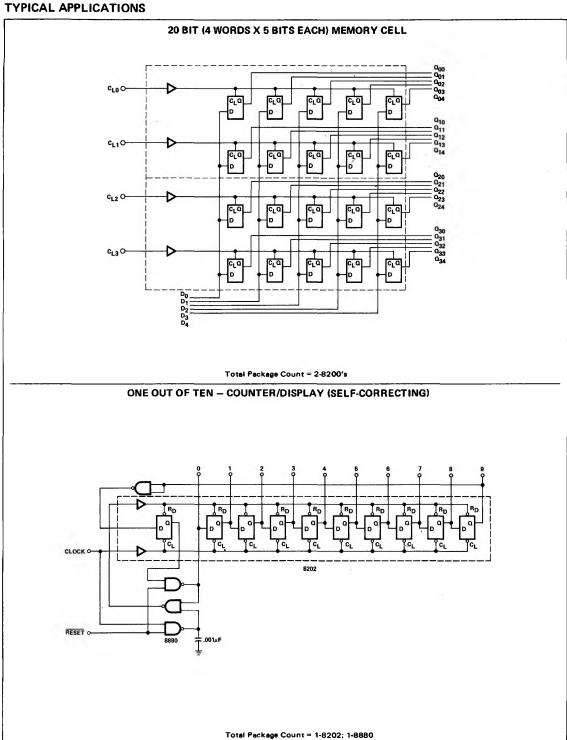

### TYPICAL APPLICATIONS (Cont'd)