No.4040

LA7282,7282M

VCR Audio Signal Recording/ Playback Processor

## Overview

The LA7282 and 7282M are small package LSIs containing all functions necessary to record and playback VTR audio signal.

### **Features**

- Smaller package leaves large space for other components.

- · Delete of In and Output electrolysis capacitor.

- Low capacitor (0.1 μF) for the line amp inputs (PE IN and AUDIO IN)

- · Non-Adjustment of PB Gain by less gain scatter

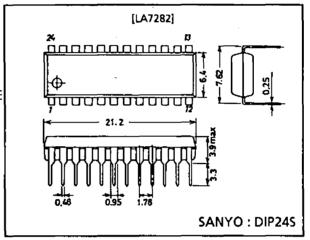

## **Package Dimensions**

unit: mm 3067-DIP24S

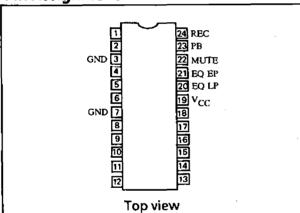

**Pin Assignment**

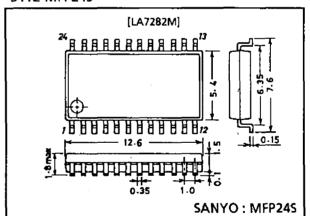

unit: mm 3112-MFP24S

| Maximum Ratings at Ta = 25°C                     |                     |                                                     |            |             | 1               | unit                 |

|--------------------------------------------------|---------------------|-----------------------------------------------------|------------|-------------|-----------------|----------------------|

| Maximum Supply Voltage                           | V <sub>CC</sub> max |                                                     |            | 14          |                 | $\mathbf{v}_{\perp}$ |

| Pin 1 Input Voltage                              | $v_{IN1}$           | Ta = 65°C, f = 80 kHz (sin),<br>$I_{LK} = 10 \mu A$ | 9          | 0 (±45)     | 7               | /р-р                 |

| Pin 1 Input Current                              | I <sub>IN1</sub>    |                                                     |            | ±1.5        |                 | mA                   |

| Allowable Power<br>Dissipation                   | Pd max              | Ta≤65°C, when mounted on the recommended PCB        |            | 400         | 1               | mW                   |

| Operating Temperature                            | Topr                |                                                     | -10        | to +65      |                 | °C                   |

| Storage Temperature                              | Tstg                |                                                     | -55        | to +125     |                 | °C                   |

| Operating Conditions at Ta = 2                   | 5°C                 |                                                     |            |             |                 | unit                 |

| Recommended Supply Voltage                       | $v_{CC}$            |                                                     |            | 12.0        |                 | V                    |

| Operating Voltage Range                          | V <sub>CC</sub> op  |                                                     | 11.25      | to 12.75    |                 | V                    |

| Operating Characteristics at Ta                  | = 25°C, V           | CC = 12  V, f = 1  kHz, OdBv = :                    |            | 61 PM       |                 |                      |

| Current Dissipation (EE)                         | Icen                | Quiescent                                           | min<br>8.0 | typ<br>12.0 | max<br>17.0     | unit<br>mA           |

| Current Dissipation (PB)                         | ICCE                | Quiescent                                           | 9.0        | 13.0        | 18.0            | mА                   |

| Current Dissipation (REC)                        | I <sub>CCP</sub>    |                                                     | 7.0        | 10.0        | 14.0            | mА                   |

| Overall Gain at PB Mode                          | I <sub>CCR</sub>    | Quiescent  FO INLINE OUT V = -5 dPv                 | 59.0       | 59.5        | 60.0            | dB                   |

| [Equalizing Amp]                                 | VG <sub>PB</sub>    | EQ IN-LINE OUT, $V_O = -5 \text{ dBv}$              | . 39.0     | 39.3        | 00.0            | uВ                   |

|                                                  | VC.                 | V = 54Dv                                            | 44.0       | 71.0        |                 | 4D                   |

| Open Loop Voltage Gain                           | VG <sub>OE</sub>    | V <sub>O</sub> = -5 dBv                             | 66.0       | 71.0        | 1.0             | dΒ                   |

| Equivalent Input Noise Voltage                   | $v_{ m NIE}$        | $Rg = 2.2 k\Omega$ , DIN Audio Filter               |            | 1.2         | 1.8             | μVrms                |

| Input Impedance                                  | $z_{INE}$           |                                                     |            | 130         |                 | kΩ                   |

| [Line Amp]                                       | 110                 |                                                     | 21.0       | 24.5        |                 |                      |

| Voltage Gain (PB IN)                             | VGLP                | $V_O = -5 \text{ dBv}$                              | 21.0       | 21.5        | 22.0            | dB                   |

| Voltage Gain (EE,REC IN)                         | VGLR                | $V_O = -5 \text{ dBv}$                              | 21.0       | 21.5        | 22.0            | ₫B                   |

| Total Harmonic Distortion                        | THDL                | $V_O = -5 \text{ dBv}$                              |            | 0.3         | 0.5             | %                    |

| Output Noise Voltage                             | v <sub>NOL</sub>    | DIN Audio Filter                                    |            | -70.0       | -64.0           | dBv                  |

| Input Impedance (PB IN)                          | Z <sub>IN1</sub>    |                                                     |            | 120         |                 | kΩ                   |

| Input Impedance (EE,REC IN)                      | $z_{IN2}$           | True and                                            |            | 120         |                 | kΩ                   |

| Maximum Output Voltage                           | VOML                | THD = 3%                                            | 1.5        | 2.1         |                 | Vrms                 |

| Output Voltage at ALC                            | $v_{OA}$            | $V_{IN} = -28 \text{ dBv}$                          | -9.0       | -8.0        | -7.0            | dBv                  |

| ALC Effect                                       | ALC                 | $V_{IN} = -28 \text{ to } -8 \text{ dBv}$           |            | 1.5         | <b>3</b> .0     | dB                   |

| Total Harmonic Distortion at ALC [Recording Amp] | THDA                | $V_{IN} = -28 \text{ dBv}$                          |            | 0.25        | 0.6             | %                    |

| Voltage Gain (open loop)                         | $v_{GOR}$           | $V_{O} = -5 \text{ dBv}$                            | 47.0       | 52.0        |                 | dB                   |

| Voltage Gain (closed loop)                       | VGCR                | $V_{O} = -5 \text{ dBv}$                            | 12.5       | 13.0        | 13.5            | đΒ                   |

| Total Harmonic Distortion                        | $THD_R$             | $V_O = -5 \text{ dBv}$                              |            | 0.1         | 0.3             | %                    |

| Input Impedance                                  | Z <sub>INR</sub>    |                                                     |            | 50          |                 | kΩ                   |

| Maximum Output Voltage                           | VOMR                | THD = 3%                                            | 1.5        | 2.0         |                 | Vrms                 |

| [Muting Circuit]                                 | Omic                |                                                     |            |             |                 |                      |

| On Voltage                                       | $v_{MON}$           | Pin 22, DC                                          | 3.8        |             | 6.0             | v                    |

| Off Voltage                                      | V <sub>MOFF</sub>   | Pin 22, DC                                          | 0          |             | 1.0             | v                    |

| Mute Attenuation Level (PB,EE)                   | $M_{P}, M_{E}$      | <b>,</b>                                            | 80.0       | 90.0        |                 | ďΒ                   |

| Mute Attenuation Level (REC)                     | M <sub>R</sub>      |                                                     | 65.0       | 70.0        |                 | dB                   |

| [PB/EE Selector Circuit]                         | K                   |                                                     |            |             |                 |                      |

| PB Mode Hold Voltage                             | $v_{pp}$            | Pin 23, DC                                          | 0          |             | 1.0             | v                    |

| EE Mode Hold Voltage                             | v <sub>PE</sub>     | Pin 23, DC                                          | 3.3        |             | 6.0             | v                    |

| [REC/EE Selector Circuit]                        | . PE                |                                                     | 5.5        |             | 0.0             | *                    |

| REC Mode Hold Voltage                            | V                   | Pin 24, DC                                          | 3.3        |             | <b>V</b>        | v                    |

| EE Mode Hold Voltage                             | V <sub>RR</sub>     |                                                     | . 0        |             | V <sub>CC</sub> | v                    |

| THE MOOR LIGHT A OFFISE                          | ${ m v}_{ m RE}$    | Pin 24, DC                                          | U          |             | 1.0             | v                    |

## LA7282,7282M

|                              |                    | •                                                                      | min | typ | max | unit |  |

|------------------------------|--------------------|------------------------------------------------------------------------|-----|-----|-----|------|--|

| [Equalizer Selector Circuit] |                    |                                                                        |     | 31  |     |      |  |

| Switch On Voltage            | $v_{EON}$          | Pin 20, 21, DC                                                         | 3.5 |     | 6.0 | v    |  |

| Switch Off Voltage           | $v_{EOFF}$         | Pin 20, 21, DC                                                         | 0   |     | 0.8 | V    |  |

| [Head Selector Switch]       |                    |                                                                        |     |     |     |      |  |

| Pin 1 On Resistance          | $R_{ON1}$          | $I1 = \pm 1 \text{ mA}$                                                |     | 15  | 30  | Ω    |  |

| Pin 2 On Resistance          | R <sub>ON2</sub>   | $I2 = \pm 1 \text{ mA}$                                                |     | 5   | 10  | Ω    |  |

| Pin 1 Input Voltage          | $\mathbf{v_{IN1}}$ | $Ta = 65^{\circ}C$ , $f = 80 \text{ kHz (sin)}$ , $I_{I.K} = 10 \mu A$ |     |     | ±45 | v    |  |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

■ Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production, SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1996. Specifications and information herein are subject to change without notice.

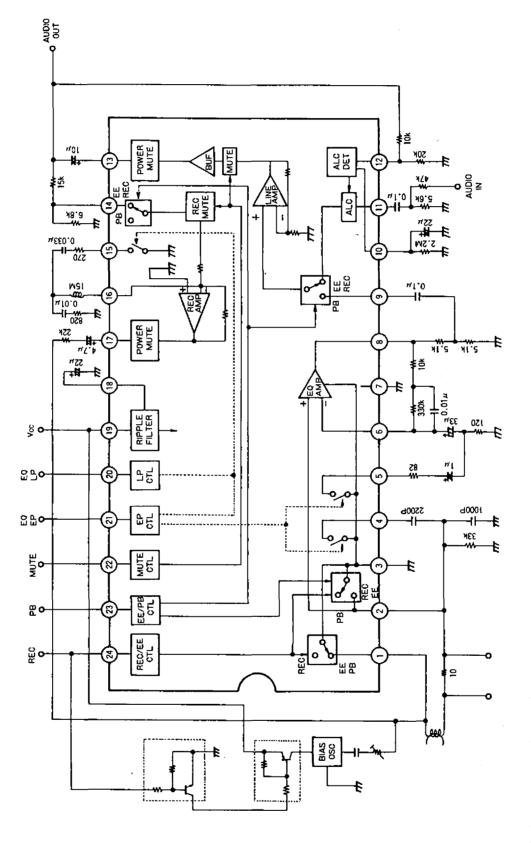

# **Block Diagram**

nit (resistance :  $\Omega$ , capacitance

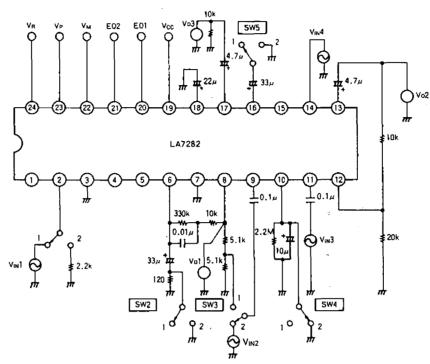

## **Test Circuit**

Unit (resistance :  $\Omega$ , capacitance : F)

## <Switch Setting Table>

| Parameter (Symbol)                      | sw <sub>1</sub> | SW2 | SW3 | SW4 | sw5 | $\mathbf{v}_{\mathbf{M}}$ | $v_{\mathbf{P}}$ | $v_R$      | Input                        | Measurement                 |

|-----------------------------------------|-----------------|-----|-----|-----|-----|---------------------------|------------------|------------|------------------------------|-----------------------------|

| ICCE                                    | 2               | 1   | 1   | 2   | 1   | GND                       | 5V               | GND        | -                            | A                           |

| I <sub>CCP</sub>                        | 2               | 1   | 1   | 2   | 1   | GND                       | GND              | GND        |                              | A                           |

| I <sub>CCR</sub>                        | 2               | 1   | 1   | 2   | 1   | GND                       | 5V               | 5 <b>V</b> | •                            | Α                           |

| VGPB                                    | 1               | 1   | 1   | 2   | 1   | GND                       | GND              | GND        | V <sub>IN</sub> 1            | V <sub>O</sub> 2            |

| · VG <sub>OE</sub>                      | 1               | 2   | 2   | 2   | 1   | GND                       | GND              | GND        | V <sub>IN</sub> 1            | v <sub>O</sub> 1            |

| v <sub>NIE</sub>                        | 2               | 1   | 2   | 2   | 1   | GND                       | GND              | GND        | -                            | V <sub>O</sub> 1            |

| $v_{G_{LP}}$ , $v_{D_L}$ , $v_{OML}$    | 2               | 1   | 2   | 2   | 1   | GND                       | GND              | GND        | V <sub>IN</sub> 2            | V <sub>O</sub> <sup>2</sup> |

| VG <sub>LR</sub>                        | 2               | 1   | 1   | 2   | 1   | GND                       | 5V               | GND        | V <sub>IN</sub> 3            | V <sub>O</sub> <sup>2</sup> |

| v <sub>NOL</sub>                        | 2               | 1   | 2   | 2   | 1   | GND                       | 5V               | GND        | -                            | v <sub>O<sup>2</sup></sub>  |

| V <sub>OA</sub> , ALC, THD <sub>A</sub> | 2               | 1   | 2   | 1   | 1   | GND                       | 5V               | GND        | V <sub>IN</sub> 3            | $v_{O^2}$                   |

| vg <sub>OR</sub>                        | 2               | 1   | 2   | 2   | 2   | GND                       | 5V               | GND        | V <sub>IN</sub> 4            | V <sub>O</sub> 3            |

| VGCR, THDR, VOMR                        | 2               | 1   | 2   | 2   | 1   | GND                       | 5V               | GND        | V <sub>IN</sub> 4            | V <sub>O</sub> 3            |

| M <sub>P</sub>                          | 1               | 1   | 1   | 2   | 1   | 5V                        | GND              | GND        | $v_{IN^1}$                   | $v_{O^2}$                   |

| M <sub>R</sub>                          | 2               | 1   | 1   | 2   | 1   | 5V                        | 5V               | GND        | V <sub>IN</sub> <sup>4</sup> | V <sub>O</sub> 3            |

| ME                                      | 2               | 1   | 2   | 2   | 1   | 5V                        | 5V               | GND        | v <sub>IN</sub> 2            | . V <sub>O</sub> 2          |

| Pin No. | Function                             | Terminal Circuit    | Description                                                                                                                                                                                                                                                              |

|---------|--------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Head Switch 1<br>(High voltage)      | Terminal Circuit    | EE, PB: on; REC: off On resistance: 10 Ω, typ. With stand voltage during off: ±45 V (f = 80 kHz)                                                                                                                                                                         |

| 2       | EQ AMP Input<br>and<br>Head Switch 2 | ②                   | Input playback signal to the head. Input impedance: 130 k $\Omega$ , typ. EE, REC: on; PB: off Switch on resistance: 5 $\Omega$ , typ.                                                                                                                                   |

| 3       | GND                                  |                     | An exclusive GND for pin 1 head switch 1, EQ AMP and playback EP switch                                                                                                                                                                                                  |

| 4       | BP Switch 1                          | 120k                | Sets the tape head resonant frequency. On resistance: 15 $\Omega$ , typ. Input impedance: 120 $k\Omega$ , typ. (playback EP mode)                                                                                                                                        |

| 5       | EP Switch 2                          | 3<br>12k            | Increases the voltage gain at higher frequencies by reducing negative feedback amount of the PB EQ AMP.  On resistance: 15 Ω, typ.  Input impedance: 12 kΩ, typ. (playback EP mode)                                                                                      |

| 6       | EQ AMP NFB                           |                     | Input of negative feedback of the EQ AMP to establish desired equalizing characteristics.                                                                                                                                                                                |

| 7       | GND                                  |                     | Common return for all circuits except for EQ AMP and head switch 1.                                                                                                                                                                                                      |

| 8       | EQ AMP Output                        | 8                   |                                                                                                                                                                                                                                                                          |

| 9       | LINE AMP PB<br>Input                 | (a) 1/20k (b) 1/20k | Input PB signal to the EQ AMP. The input impedance of pin 9 i high (120 k $\Omega$ ) and requires a small coupling capacitor of 0.1 $\mu F$ .                                                                                                                            |

| 10      | ALC FILTER                           | 10 200 m            | Connecting this pin to GND through a capacitor enables detection. The RC time constant sets attack recovery time.                                                                                                                                                        |

| 11      | LINE AMP<br>Audio Input              |                     | Input EE, REC signal. Select value of $R_1$ and $R_2$ so that the reference input is at the shoulder of the ALC. The amp gain should be set for 21.5 dB. The input impedance of pin 11 is high (120 k $\Omega$ ) and requires a small coupling capacitor of 0.1 $\mu$ F. |

| 12      | ALC Detect Input                     | 120k # 777          | Accepts the output signal of LINE amp. The ALC level is determined by the voltage divider consisting of R <sub>1</sub> and R <sub>2</sub> .                                                                                                                              |

| 13      | LINE AMP<br>Output                   | 13—                 | Output impedance: 50 $\Omega$ , typ.                                                                                                                                                                                                                                     |

Unit (resistance : Ω)

| Pin No. | Function                             | Terminal Circuit                       | Description                                                                                                                                                                                                                         |

|---------|--------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      |                                      | Telininai Circult                      | Description  Leave to a size of fear LINE, AMP                                                                                                                                                                                      |

| 14      | REC AMP Input                        | 14) 36k                                | Input recording signal from LINE AMP.  Input current is set by the divider consisting of R <sub>1</sub> and R <sub>2</sub> .  Pin 14 requires no coupling capacitor since REC AMP is to operate at zero level and as inverting amp. |

| 15      | LP Switch                            | 60k m                                  | Sets the high peaking point to the frequency suitable for LP. On resistance: 15 $\Omega$ typ. Input impedance: 60 k $\Omega$ typ.                                                                                                   |

| 16      | REC AMP NFB                          | RNF RE I.5k                            | Connecting an L, C, R network to this pin causes a peaking frequency to rise.                                                                                                                                                       |

| 17      | REC AMP<br>Output                    | ************************************** | Output impedance: 40 Ω typ.                                                                                                                                                                                                         |

| 18      | Ripple Filter                        | Each AMP Voc                           | Connecting a electrolytic capacitor across this pin and GND smoothes ripples.                                                                                                                                                       |

| 19      | Supply Voltage<br>(V <sub>CC</sub> ) |                                        | $V_{CC} = 15 \text{ V max}$ $V_{CC} = 11.25 - 12.75 \text{ V typ.}$                                                                                                                                                                 |

| 20      | LP Control                           | 300k                                   | Applying 3.5 V DC or more (6.0 V max.) to this pin turns on LP switch (pin 15). The switch turns off at 0.8 V or below.                                                                                                             |

| 21      | EP Control                           | 2) 10k                                 | Applying 3.5 V DC or more (6.0 V max.) to this pin turns on EP switch (pin 4,5) and LP switch (pin 15). The switches turn off at 0.8 V or below.                                                                                    |

| 22      | MUTE Control                         | 100k                                   | Applying 3.8 V DC or more (6.0 V max.) to this pin turns on mute circuit. The mute is disabled at 1.0 V or below.  [Control mode]    Mode                                                                                           |

| 23      | PB Control                           | 23 10k 0 T                             | Applying 3.3 V DC or more (6.0 V max.) to this pin enters EE mode and 1.0 V or below PB mode.                                                                                                                                       |

| 24      | REC Control                          | 20 10k                                 | Applying 3.0 V DC or more (up to $V_{CC}$ ) to this pin enters REC mode and 1.0 V or below EE mode.                                                                                                                                 |

|         |                                      | Unit (resistance : Ω)                  |                                                                                                                                                                                                                                     |