LM3528

# LM3528 High Efficiency, Multi Display LED Driver with 128 Exponential Dimming Steps and Integrated OLED Power Supply in a 1.2mm × 1.6mm DSBGA Package

Check for Samples: LM3528

# FEATURES

- **128 Exponential Dimming Steps**

- **Programmable Auto-Dimming Function**

- Up to 90% Efficient

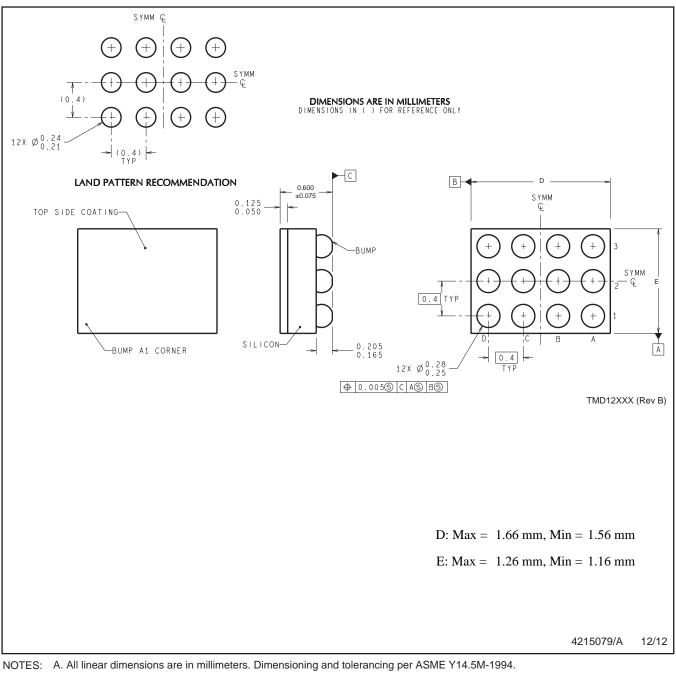

- Low Profile 12 Bump DSBGA Package (1.2mm x 1.6mm x 0.6mm)

- Integrated OLED Display Power Supply and LED Driver

- **Programmable Pattern Generator Output for LED Indicator Function**

- Drives up to 12 LED's at 20mA

- Drives up to 5 LED's at 20mA and delivers 18V at 40mA

- **1% Accurate Current Matching Between** Strings

- Internal Soft-Start Limits Inrush Current

- True Shutdown Isolation for LED's

- Wide 2.5V to 5.5V Input Voltage Range •

- 22V Over-Voltage Protection •

- **1.25MHz Fixed Frequency Operation** •

- **Dedicated Programmable General Purpose I/O**

- **Active Low Hardware Reset**

# APPLICATIONS

- **Dual Display LCD Backlighting for Portable** ٠ Applications

- Large Format LCD Backlighting

- **OLED Panel Power Supply** ٠

- **Display Backlighting with Indicator Light**

# DESCRIPTION

The LM3528 current mode boost converter offers two separate outputs. The first output (MAIN) is a constant current sink for driving series white LED's. The second output (SUB/FB) is configurable as a constant current sink for series white LED bias, or as a feedback pin to set a constant output voltage for powering OLED panels.

As a dual output white LED bias supply, the LM3528 adaptively regulates the supply voltage of the LED strings to maximize efficiency and insure the current sinks remain in regulation. The maximum current per output is set via a single external low power resistor. An I<sup>2</sup>C compatible interface allows for independent adjustment of the LED current in either output from 0 to max current in 128 exponential steps. When configured as a white LED + OLED bias supply the LM3528 can independently and simultaneously drive a string of up to 6 white LED's and deliver a constant output voltage of up to 21V for OLED panels.

Output over-voltage protection shuts down the device if V<sub>OUT</sub> rises above 22V allowing for the use of small sized low voltage output capacitors. Other features include a dedicated general purpose I/O (GPIO) and a multifunction pin (HWEN/PGEN/GPIO) which can be configured as a 32 bit pattern generator, a hardware enable input, or as a GPIO. When configured as a pattern generator, an arbitrary pattern is programmed via the I<sup>2</sup>C compatible interface and output at HWEN/PGEN/GPIO for indicator LED flashing or for external logic control. The LM3528 is offered in a tiny 12-bump DSBGA package and operates over the -40°C to +85°C temperature range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# LM3528

# SNVS513A - AUGUST 2008 - REVISED AUGUST 2012

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

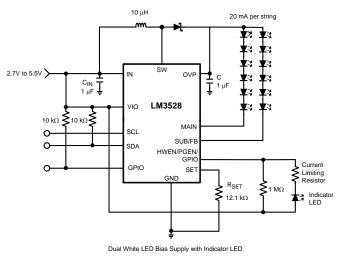

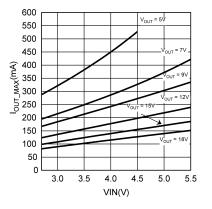

**Figure 1. Typical Application Circuit**

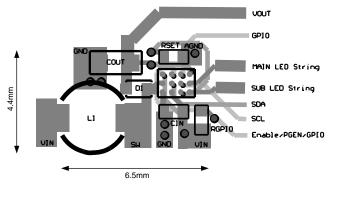

Figure 2. Typical PCB Layout

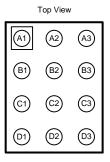

# **Connection Diagram**

# **PIN DESCRIPTIONS**

| Pin | Name               | Function                                                                                                                                                                                                   |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | OVP                | Over-Voltage Protection Sense Connection. Connect OVP to the positive terminal of the output capacitor.                                                                                                    |

| A2  | MAIN               | Main Current Sink Input.                                                                                                                                                                                   |

| A3  | SUB/FB             | Secondary Current Sink Input or 1.21V Feedback Connection for Constant Voltage Output.                                                                                                                     |

| B1  | GPIO1              | Programmable General Purpose I/O.                                                                                                                                                                          |

| B2  | SCL                | Serial Clock Input                                                                                                                                                                                         |

| B3  | SET                | LED Current Setting Connection. Connect a resistor from SET to GND to set the maximum LED current into MAIN or SUB/FB (when in LED mode), where $I_{LED_MAX} = 192 \times 1.244 \text{V/R}_{\text{SET}}$ . |

| C1  | HWEN/PGEN/GPI<br>O | Active High Hardware Enable Input. Programmable Pattern Generator Output, and Programmable General Purpose I/O.                                                                                            |

| C2  | SDA                | Serial Data Input/Output                                                                                                                                                                                   |

| C3  | IN                 | Input Voltage Connection. Connect IN to the input supply, and bypass to GND with a $1\mu F$ ceramic capacitor.                                                                                             |

| D1  | VIO                | Logic Voltage Level Input                                                                                                                                                                                  |

| D2  | SW                 | Drain Connection for Internal NMOS Switch                                                                                                                                                                  |

#### www.ti.com

#### **PIN DESCRIPTIONS (continued)**

| Pin | Name | Function |

|-----|------|----------|

| D3  | GND  | Ground   |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)

| -0.3V to 6V        |

|--------------------|

| -0.3V to 25V       |

| -0.3V to 23V       |

| -0.3V to 6V        |

| Internally Limited |

| +150°C             |

| -65°C to +150°C    |

| +300°C             |

| 2.5kV              |

|                    |

(1) Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

(3) All voltages are with respect to the potential at the GND pin.

(4) For detailed soldering specifications and information, please refer to Texas Instruments Application Note 1112: DSBGA Wafer LEvel Chip Scale Package (AN-1112).

(5) The human body model is a 100pF capacitor discharged through 1.5kΩ resistor into each pin. (MIL-STD-883 3015.7).

# **Operating Ratings** <sup>(1)(2)</sup>

| V <sub>IN</sub>                                            | 2.5V to 5.5V    |

|------------------------------------------------------------|-----------------|

| V <sub>SW</sub> , V <sub>OVP</sub> ,                       | 0V to 23V       |

| V <sub>SUB/FB</sub> , V <sub>MAIN</sub>                    | 0V to 21V       |

| Junction Temperature Range $(T_J)^{(3)}$                   | -40°C to +110°C |

| Ambient Temperature Range (T <sub>A</sub> ) <sup>(4)</sup> | -40°C to +85°C  |

(1) Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

(2) All voltages are with respect to the potential at the GND pin.

- (3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub>=+150°C (typ.) and disengages at T<sub>J</sub>=+140°C (typ.).

- (4) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (TJ-MAX-OP = +105°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

# **Thermal Properties**

| Junction to Ambient Thermal Resistance $(\theta_{JA})^{(1)}$ | 68°C/W |

|--------------------------------------------------------------|--------|

|                                                              |        |

(1) Junction-to-ambient thermal resistance (θ<sub>JA</sub>) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 114.3mm x 76.2mm x 1.6mm. The ground plane on the board is 113mm x 75mm. Thickness of copper layers are 71.5µm/35µm/35µm/71.5µm (2oz/1oz/2oz). Ambient temperature in simulation is 22°C, still air. Power dissipation is 1W. For more information on these topics, please refer to Texas Instruments Application Note 1112, and JEDEC Standard JESD51-7.

# **Electrical Characteristics**

Specifications in standard type face are for  $T_A = 25^{\circ}$ C and those in **boldface type** apply over the Operating Temperature Range of  $T_A = -40^{\circ}$ C to +85°C. Unless otherwise specified  $V_{IN} = 3.6$ V,  $V_{IO} = 1.8$ V,  $V_{\overline{RESET}/GPIO} = V_{IN}$ ,  $V_{SUB/FB} = V_{MAIN} = 0.5$ V,  $R_{set} = 12.0$ k $\Omega$ , OLED = '0', ENM = ENS = '1', BSUB = BMAIN = Full Scale.<sup>(1)</sup>

| Symbol                             | Parameter                                                    | Conditions                                                                                                                                                | Min                 | Тур          | Max                  | Units |

|------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|----------------------|-------|

| I <sub>LED</sub>                   | Output Current Regulation<br>MAIN or SUB/FB Enabled          | UNI = '0', or '1',<br>2.5V < V <sub>IN</sub> < 5.5V                                                                                                       | 18.5                | 20           | 22                   |       |

|                                    | Maximum Current Per<br>Current Sink                          | $R_{SET} = 8.0 k\Omega$                                                                                                                                   |                     | 30           |                      | mA    |

| ILED-MATCH                         | I <sub>MAIN</sub> to I <sub>SUB/FB</sub> Current<br>Matching | UNI = '1',<br>2.5V < V <sub>IN</sub> < 5.5V <sup>(3)</sup>                                                                                                |                     | 0.15         | 1                    | %     |

| V <sub>SET</sub>                   | SET Pin Voltage                                              | $3.0V < V_{IN} < 5V$                                                                                                                                      |                     | 1.244        |                      | V     |

| I <sub>LED</sub> /I <sub>SET</sub> | $I_{LED}$ Current to $I_{SET}$ Current Ratio                 |                                                                                                                                                           |                     | 192          |                      |       |

| V <sub>REG_CS</sub>                | Regulated Current Sink<br>Headroom Voltage                   |                                                                                                                                                           |                     | 500          |                      | mV    |

| V <sub>REG_OLED</sub>              | V <sub>SUB/FB</sub> Regulation Voltage in OLED Mode          | 2.5V < V <sub>IN</sub> < 5.5V, OLED =<br>'1'                                                                                                              | 1.170               | 1.21         | 1.21 <b>1.237</b>    |       |

| V <sub>HR</sub>                    | Current Sink Minimum<br>Headroom Voltage                     | $I_{LED} = 95\%$ of nominal                                                                                                                               |                     | 300          |                      | mV    |

| R <sub>DSON</sub>                  | NMOS Switch On Resistance                                    | I <sub>SW</sub> = 100mA                                                                                                                                   |                     | 0.43         |                      | Ω     |

| I <sub>CL</sub>                    | NMOS Switch Current Limit                                    | 2.5V < V <sub>IN</sub> < 5.5V                                                                                                                             | 645                 | 770          | 900                  | mA    |

| V <sub>OVP</sub>                   | Output Over-Voltage<br>Protection                            | ON Threshold,<br>2.5V < V <sub>IN</sub> < 5.5V                                                                                                            | 20.6                | 22 <b>23</b> |                      | V     |

|                                    |                                                              | OFF Threshold,<br>2.7V < $V_{IN}$ < 5.5V                                                                                                                  | 19.25               | 20.6         | 21.5                 | v     |

| f <sub>SW</sub>                    | Switching Frequency                                          |                                                                                                                                                           | 1.0                 | 1.27         | 1.4                  | MHz   |

| D <sub>MAX</sub>                   | Maximum Duty Cycle                                           |                                                                                                                                                           |                     | 90           |                      | %     |

| D <sub>MIN</sub>                   | Minimum Duty Cycle                                           |                                                                                                                                                           |                     | 10           |                      | %     |

| Ι <sub>Q</sub>                     | Quiescent Current, Device<br>Not Switching                   | $ \begin{array}{l} V_{MAIN} \text{ and } V_{SUB/FB} > \\ V_{REG\_CS}, \\ BSUB = BMAIN = 0x00, \ 2.5V \\ < V_{IN} < 5.5V \end{array} $                     |                     | 350          | 390                  |       |

|                                    |                                                              | $\label{eq:substant} \begin{array}{l} V_{SUB/FB} > V_{REG\_OLED}, \\ OLED='1', ENM=ENS='0', \\ R_{SET} \mbox{ Open}, \\ 2.5V < V_{IN} < 5.5V \end{array}$ |                     | 250          | 260                  | μA    |

| I <sub>SHDN</sub>                  | Shutdown Current                                             | ENM = ENS = OLED = '0',<br>2.5V < V <sub>IN</sub> < 5.5V                                                                                                  |                     | 1.8          | 3                    | μA    |

| HWEN/PGEN/G                        | PIO, GPIO1 Pin Voltage Specific                              | ations                                                                                                                                                    |                     |              |                      |       |

| V <sub>IL</sub>                    | Input Logic Low                                              | $2.5V < V_{IN} < 5.5V$ , MODE bit = 0                                                                                                                     |                     |              | 0.5                  | V     |

| V <sub>IH</sub>                    | Input Logic High                                             | 2.5V < V <sub>IN</sub> < 5.5V, MODE bit<br>= 0                                                                                                            | 1.1                 |              |                      | V     |

| V <sub>OL</sub>                    | Output Logic Low                                             | $I_{LOAD}$ =3mA, MODE bit = 1                                                                                                                             |                     |              | 400                  | mV    |

| I <sup>2</sup> C Compatible        | Voltage Specifications (SCL, SE                              | DA, VIO)                                                                                                                                                  |                     |              |                      |       |

| V <sub>IO</sub>                    | Serial Bus Voltage Level                                     | $2.5V < V_{IN} < 5.5V^{(4)}$                                                                                                                              | 1.7                 |              | V <sub>IN</sub>      | V     |

| VIL                                | Input Logic Low                                              | 2.5V < V <sub>IN</sub> < 5.5V                                                                                                                             |                     |              | 0.36×V <sub>IO</sub> | V     |

| V <sub>IH</sub>                    | Input Logic High                                             | 2.5V < V <sub>IN</sub> < 5.5V                                                                                                                             | 0.7×V <sub>IO</sub> |              |                      | V     |

(1) All voltages are with respect to the potential at the GND pin.

(2) Min and Max limits are guaranteed by design, test, or statistical analysis. Typical (Typ) numbers are not guaranteed, but represent the most likely norm.

(3) The matching specification between MAIN and SUB is calculated as 100 × ((I<sub>MAIN</sub> or I<sub>SUB</sub>) - I<sub>AVE</sub>) / I<sub>AVE</sub>. This simplifies out to be 100 × (I<sub>MAIN</sub> - I<sub>SUB</sub>)/(I<sub>MAIN</sub> + I<sub>SUB</sub>).

(4) SCL and SDA signals are referenced to VIO and GND for minimum VIO voltage testing. VIO limits indicate the minimum voltage at VIO at which the part is operational.

www.ti.com

# **Electrical Characteristics (continued)**

Specifications in standard type face are for  $T_A = 25^{\circ}$ C and those in **boldface type** apply over the Operating Temperature Range of  $T_A = -40^{\circ}$ C to +85°C. Unless otherwise specified  $V_{IN} = 3.6V$ ,  $V_{IO} = 1.8V$ ,  $V_{RESET/GPIO} = V_{IN}$ ,  $V_{SUB/FB} = V_{MAIN} = 0.5V$ ,  $R_{set} = 12.0$ k $\Omega$ , OLED = '0', ENM = ENS = '1', BSUB = BMAIN = Full Scale.<sup>(1)</sup> (2)</sup>

| Symbol                      | Parameter                                   | Conditions                              | Min | Тур | Max | Units |

|-----------------------------|---------------------------------------------|-----------------------------------------|-----|-----|-----|-------|

| V <sub>OL</sub>             | Output Logic Low                            | I <sub>LOAD</sub> = 3mA                 |     |     | 400 | mV    |

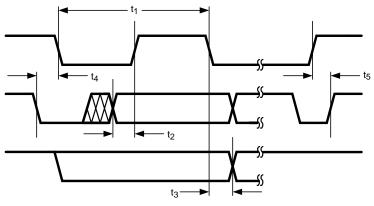

| I <sup>2</sup> C Compatible | Timing Specifications (SCL, SD              | A, VIO, see Figure 4) <sup>(5)(4)</sup> | L.  |     |     |       |

| t <sub>1</sub>              | SCL Clock Period                            |                                         | 2.5 |     |     | μs    |

| t <sub>2</sub>              | Data In Setup Time to SCL<br>High           |                                         | 100 |     |     | ns    |

| t <sub>3</sub>              | Data Out Stable After SCL<br>Low            |                                         | 0   |     |     | ns    |

| t4                          | SDA Low Setup Time to SCL<br>Low (Start)    |                                         | 100 |     |     | ns    |

| t <sub>5</sub>              | SDA High Hold Time After<br>SCL High (Stop) |                                         | 100 |     |     | ns    |

(5) SCL and SDA must be glitch-free in order for proper brightness control to be realized.

# **Timing Diagram**

Figure 4. I<sup>2</sup>C Timing

www.ti.com

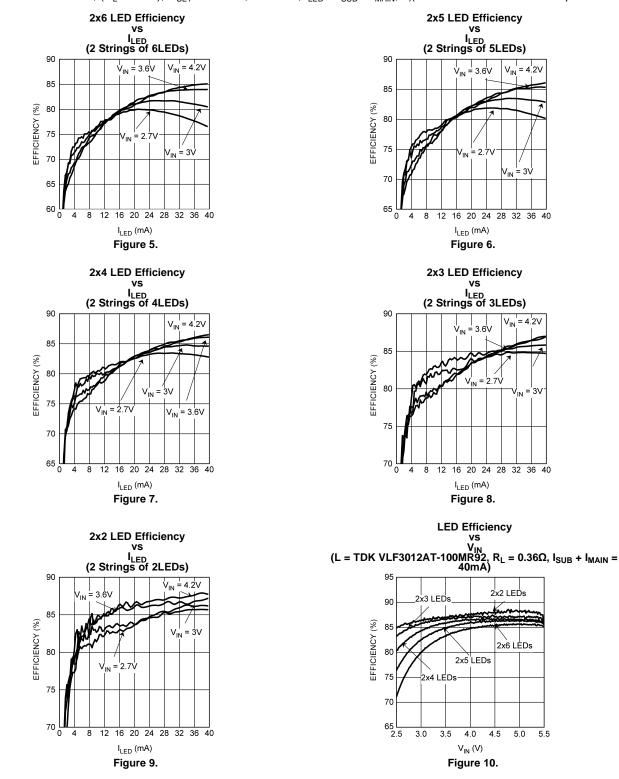

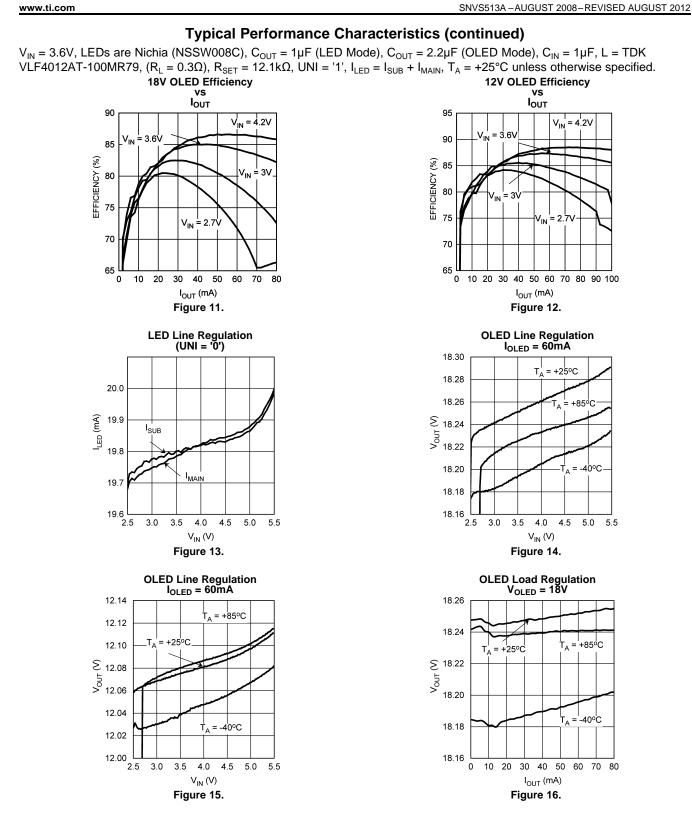

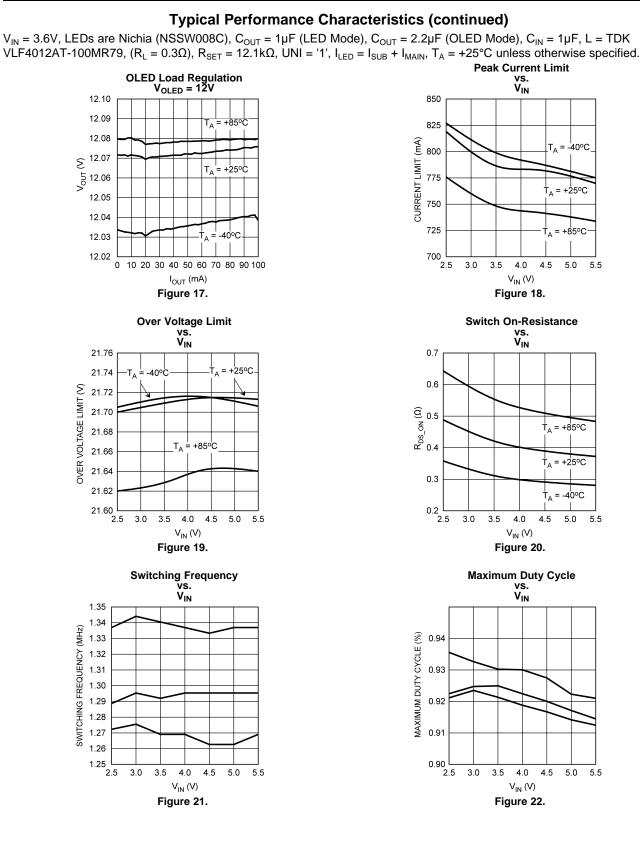

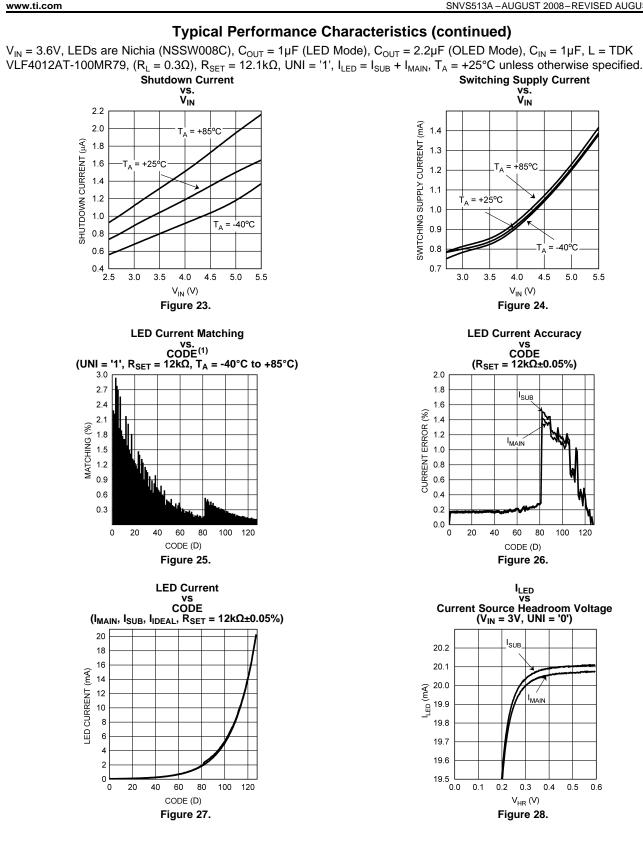

$V_{\text{IN}} = 3.6\text{V}, \text{LEDs are Nichia (NSSW008C)}, C_{\text{OUT}} = 1\mu\text{F} (\text{LED Mode}), C_{\text{OUT}} = 2.2\mu\text{F} (\text{OLED Mode}), C_{\text{IN}} = 1\mu\text{F}, L = \text{TDK} \\ \text{VLF4012AT-100MR79}, (R_{\text{L}} = 0.3\Omega), R_{\text{SET}} = 12.1\text{k}\Omega, \text{UNI} = '1', I_{\text{LED}} = I_{\text{SUB}} + I_{\text{MAIN}}, T_{\text{A}} = +25^{\circ}\text{C} \text{ unless otherwise specified}.$

TEXAS INSTRUMENTS

www.ti.com

8

(1) The matching specification between MAIN and SUB is calculated as 100 x ((I<sub>MAIN</sub> or I<sub>SUB</sub>) - I<sub>AVE</sub>) / I<sub>AVE</sub>. This simplifies out to be 100 x  $(I_{MAIN} - I_{SUB})/(I_{MAIN} + I_{SUB}).$

STRUMENTS

EXAS

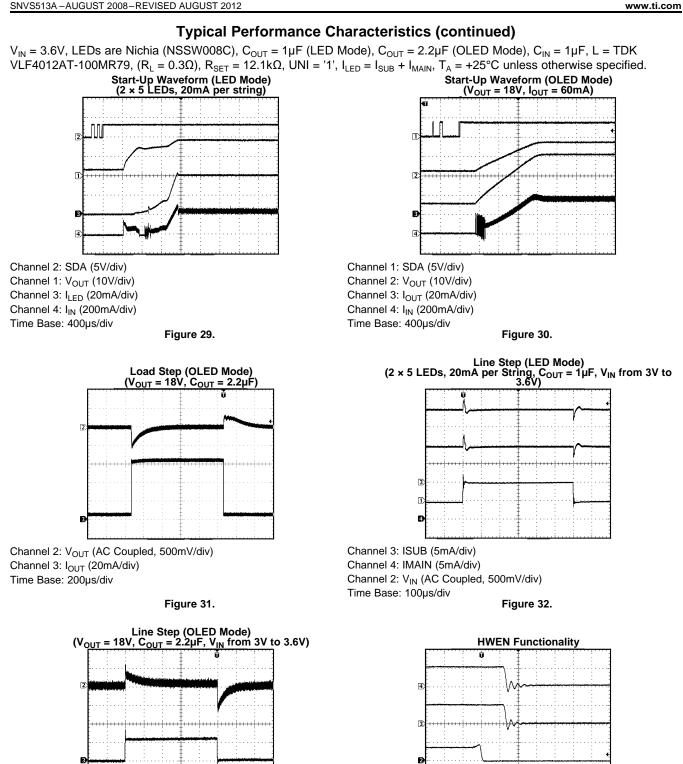

Channel 2: VOUT (AC Coupled, 100mV/div) Channel 3: VIN (AC Coupled, 500mV/div) Time Base: 200µs/div

Copyright © 2008–2012, Texas Instruments Incorporated

Figure 34.

Channel 4: I<sub>SUB</sub> (20mA/div)

Channel 3: I<sub>MAIN</sub> (20mA/div)

Channel 2: HWEN (5V/div) Time Base: 200ns/div

www.ti.com

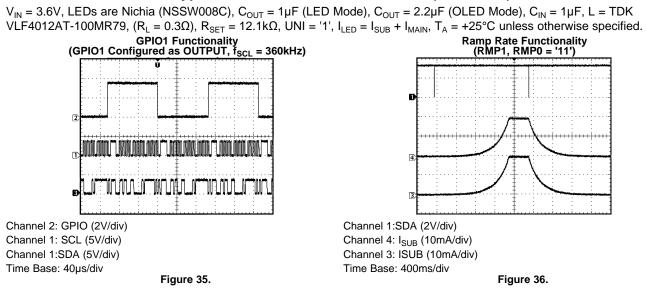

# **Typical Performance Characteristics (continued)**

TEXAS INSTRUMENTS

SNVS513A - AUGUST 2008 - REVISED AUGUST 2012

www.ti.com

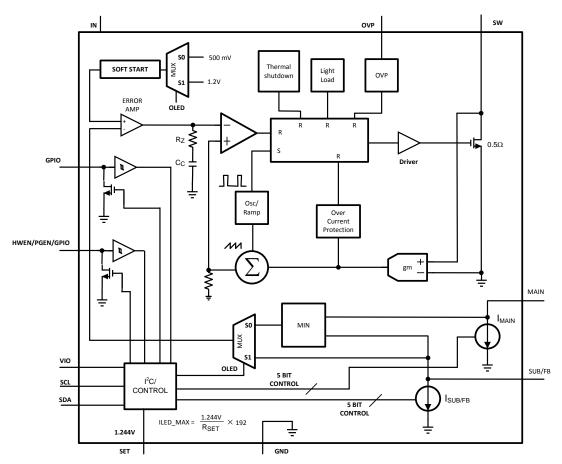

Figure 37. LM3528 Block Diagram

# **OPERATION DESCRIPTION**

The LM3528 Current Mode PWM boost converter operates from a 2.7V to 5.5V input and provides two regulated outputs for White LED and OLED display biasing. The first output, MAIN, provides a constant current of up to 30mA to bias up to 6 series white LED's. The second output, SUB/FB, can be configured as a current source for up to 6 series white LED's at at up to 30mA, or as a feedback voltage pin to regulate a constant output voltage of up to 21V. When both MAIN and SUB/FB are configured for white LED bias the current for each LED string is controlled independently or in unison via an I<sup>2</sup>C-compatible interface. When MAIN is configured for white LED bias and SUB/FB is configured as a feedback voltage pin, the current into MAIN is controlled via the I<sup>2</sup>C-compatible interface and SUB/FB becomes the middle tap of a resistive divider used to regulate the output voltage of the boost converter.

The core of the LM3528 is a Current Mode Boost converter. Operation is as follows. At the start of each switching cycle the internal oscillator sets the PWM converter. The converter turns the NMOS switch on, allowing the inductor current to ramp while the output capacitor supplies power to the white LED's and/or OLED panel. The error signal at the output of the error amplifier is compared against the sensed inductor current. When the sensed inductor current equals the error signal, or when the maximum duty cycle is reached, the NMOS switch turns off causing the external Schottky diode to pick up the inductor current. This allows the inductor current to ramp down causing its stored energy to charge the output capacitor and supply power to the load. At the end of the clock period the PWM controller is again set and the process repeats itself.

### Adaptive Regulation

When biasing dual white led strings (White LED mode) the LM3528 maximizes efficiency by adaptively regulating the output voltage. In this configuration the 500mV reference is connected to the non-inverting input of the error amplifier via mux S2 (see Figure 37). The lowest of either  $V_{MAIN}$  or  $V_{SUB/FB}$  is then applied to the inverting input of the error amplifier via mux S1. This ensures that  $V_{MAIN}$  and  $V_{SUB/FB}$  are at least 500mV, thus providing enough voltage headroom at the input to the current sinks for proper current regulation.

In the instance when there are unequal numbers of LEDs or unequal currents from string to string, the string with the highest voltage will be the regulation point.

# Unison/Non-Unison Mode

Within White LED mode there are two separate modes of operation, Unison and Non-Unison. Non-Unison mode provides for independent current regulation, while Unison mode gives up independent regulation for more accurate matching between LED strings. When in Non-Unison mode the LED currents  $I_{MAIN}$  and  $I_{SUB/FB}$  are independently controlled via registers BMAIN and BSUB respectively (see Brightness Registers (BMAIN and BSUB) section). When in Unison mode BSUB is disabled and both  $I_{MAIN}$  and  $I_{SUB/FB}$  are controlled via BMAIN only.

# Start-Up

The LM3528 features an internal soft-start, preventing large inrush currents during start-up that can cause excessive voltage ripple on the input. For the typical application circuits when the device is brought out of shutdown the average input current ramps from zero to 450mA in approximately 1.2ms. See Start Up Plots in the Typical Performance Characteristics.

### OLED Mode

When the LM3528 is configured for a single White LED bias + OLED display bias (OLED mode), the noninverting input of the error amplifier is connected to the internal 1.21V reference via MUX S2. MUX S1 switches SUB/FB to the inverting input of the error amplifier while disconnecting the internal current sink at SUB/FB. The voltage at MAIN is not regulated in OLED mode so when the application requires white LED + OLED panel biasing, ensure that at least 300mV of headroom is maintained at MAIN to guarantee proper regulation of  $I_{MAIN}$ . (see the Typical Performance Characteristics for a plot of  $I_{LED}$  vs Current Source Headroom Voltage)

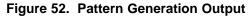

# Peak Current Limit

The LM3528's boost converter has a peak current limit for the internal power switch of 770mA typical (650mA minimum). When the peak switch current reaches the current limit the duty cycle is terminated resulting in a limit on the maximum output current and thus the maximum output power the LM3528 can deliver. Calculate the maximum LED current as a function of  $V_{IN}$ ,  $V_{OUT}$ , L and  $I_{PEAK}$  as:

$$I_{OUT\_MAX} = \frac{(I_{PEAK} - \Delta I_L) \times \eta \times V_{IN}}{V_{OUT}}$$

where

$$\Delta I_L = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{2 \times f_{SW} \times L \times V_{OUT}}$$

(1)

$f_{SW}$  = 1.27MHz. Typical values for efficiency and I<sub>PEAK</sub> can be found in the efficiency and I<sub>PEAK</sub> curves in the Typical Performance Characteristics.

# **Over Voltage Protection**

The LM3528's output voltage ( $V_{OUT}$ ) is limited on the high end by the Output Over-Voltage Protection Threshold ( $V_{OVP}$ ) of 21.2V (min). In White LED mode during output open circuit conditions the output voltage will rise to the over voltage protection threshold. When this happens the controller will stop switching causing  $V_{OUT}$  to droop. When the output voltage drops below 19.7V (min) the device will resume switching. If the device remains in an over voltage condition the LM3528 will repeat the cycle causing the output to cycle between the high and low OVP thresholds. See waveform for OVP condition in the Typical Performance Characteristics.

Copyright © 2008–2012, Texas Instruments Incorporated

# **Output Current Accuracy and Current Matching**

The LM3528 provides both precise current accuracy (% error from ideal value) and accurate current matching between the MAIN and SUB/FB current sinks. Two modes of operation affect the current matching between  $I_{MAIN}$  and  $I_{SUB/FB}$ . The first mode (Non-Unison mode) is set by writing a 0 to bit 2 of the General Purpose register (UNI bit). Non-Unison mode allows for independent programming of  $I_{MAIN}$  and  $I_{SUB/FB}$  via registers BMAIN and BSUB respectively. In this mode typical matching between current sinks is 1%.

Writing a 1 to UNI configures the device for Unison mode. In Unison mode, BSUB is disabled and  $I_{MAIN}$  and  $I_{SUB/FB}$  are both controlled via register BMAIN. In this mode typical matching is 0.15%.

# Light Load Operation

The LM3528 boost converter operates in three modes; continuous conduction, discontinuous conduction, and skip mode operation. Under heavy loads when the inductor current does not reach zero before the end of the switching period the device switches at a constant frequency. As the output current decreases and the inductor current reaches zero before the end of the switching cycle, the device operates in discontinuous conduction. At very light loads the LM3528 will enter skip mode operation causing the switching period to lengthen and the device to only switch as required to maintain regulation at the output.

# Hardware Enable/Pattern Generator/General Purpose I/O (HWEN/PGEN/GPIO)

HWEN/PGEN/GPIO can be configured for three different modes of operation; Hardware Enable, Pattern Generation, and General Purpose I/O. Register HPG at address 0x80 controls the functionality of this pin (see Table 6).

### Hardware Enable (HWEN)

On initial power-up HWEN/PGEN/GPIO defaults to the Hardware Enable (HWEN) state. In this mode HWEN/PGEN/GPIO is an active high open-drain input enable to the device. When in HWEN mode HWEN/PGEN/GPIO must be pulled up to at least 0.7 × VIO to enable the device. In HWEN mode pulling HWEN/PGEN/GPIO below 0.36 × VIO will shutdown the LM3528, resetting all registers, and forcing MAIN, SUB/FB, and SW high impedance. Bit 0 of the HPG register controls the HWEN function. Writing a '0' to this bit enables the HWEN mode. Writing a '1' to this bit disables the HWEN mode and allows selection between the other two modes.

# Pattern Generator (PGEN)

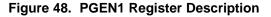

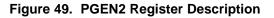

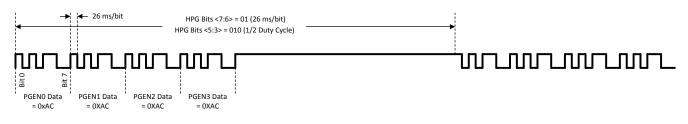

With bit 0 of the HPG register set to 1, HWEN/PGEN/GPIO can be programmed as an open drain Pattern Generator Output (PGEN). In PGEN mode a 32 bit pattern is output at HWEN/PGEN/GPIO. This pattern can be programmed to repeat itself at 4 different frequencies and 6 different duty cycles. The arbitrary pattern is programmed into four 8 bit registers; PGEN0 (address 0x90), PGEN1 (address 0x91), PGEN2 (address 0x92), and PGEN3 (address 0x93) (see Figure 47 - Figure 50). Figure 51 details an example of a 32 bit pattern at a specific programmed duty cycle and frequency. A '1' written to the PGEN\_ registers forces HWEN/PGEN/GPIO low. A '0' causes HWEN/PGEN/GPIO to go open drain.

Bits <5:3> in the HPG register have three functions; GPIO enable, duty cycle select, and pattern latch. Any combination of these bits other than '000' or '111' puts HWEN/PGEN/GPIO into PGEN mode at the specified duty cycle shown in Table 6. Writing a '111' to bits <5:3> latches the 32 bit pattern programmed into the 4 pattern generator registers PGEN0, PGEN1, PGEN2, PGEN3 into the internal shift register. When bits <5:3> = '000' the PGEN mode is off and HWEN/PGEN/GPIO is configured as a GPIO.

Bits <7:6> of the HPG register control the pattern frequency. See Table 6 for the detailed breakdown of each available frequency. Figure 51 details the pattern programming and Figure 52 shows the pattern output at HWEN/PGEN/GPIO.

# General Purpose I/O (GPIO1)

With bits <5:3> and bit 0 of the HPG register all set to '0' HWEN/PGEN/GPIO functions as an open drain General Purpose I/O. In this mode, bit 1 of the HPG register controls the logic direction (Input or Output) and bit 2 holds the logic data. With bit 1 set to '0' HWEN/PGEN/GPIO is configured as an output. In this mode a '0' written to bit 2 forces HWEN/PGEN/GPIO to logic low. Likewise, a '1' written to bit 2 will force HWEN/PGEN/GPIO open drain. When bit 1 is set to '1' HWEN/PGEN/GPIO is configured as a logic input. In this

mode when HWEN/PGEN/GPIO is externally pulled low a '0' is written to bit 2 of the HPG register. Likewise, when HWEN/PGEN/GPIO is externally pulled high a '1' is written to bit 2 of the HPG register. Table 6 and Figure 45 detail the bit functions of the HPG register and their power-on-reset values. Note that the logic output levels for the GPIO function of this pin are inverted compared to the PGEN functions. For example, a 1 written to the PGEN registers cause the HWEN/PGEN/GPIO pin to pull low while a 1 written to the bit 2 of the HPG register causes the pin to go open drain.

# General Purpose I/O (GPIO0)

The GPIO pin is a dedicated General Purpose I/O (open drain) and is controlled via the GPIO register at address 0x81. Bit 1 holds the logic data while bit 0 controls the logic direction (Input or Output). Bits <7:2> are un-used and will always read back as logic '1'. With bit 0 set to '0' GPIO is configured as an output. In this mode a '0' written to bit 1 forces GPIO to a logic low. Likewise, a '1' written to bit 1 will force GPIO to logic high. When bit 0 is set to '1' GPIO is configured as a logic input. In this mode when GPIO is externally pulled low a '0' is written to bit 1 of the GPIO register. Likewise, when GPIO is externally pulled high a '1' is written to bit 2 of the HPG register. Table 8 and Figure 46 detail the bit functions and power-on-reset values of GPIO.

During an initial GPIO write two I2C sequences (Slave I.D, Register Address, Register Data) are required to change the state of the GPIO pin. The first write configures the GPIO pin as an output. The second write will change the state of the GPIO output to the desired logic '1' or '0'.

# **Thermal Shutdown**

The LM3528 offers a thermal shutdown protection. When the die temperature reaches +140°C the device will shutdown and not turn on again until the die temperature falls below +120°C.

# I<sup>2</sup>C Compatible Interface

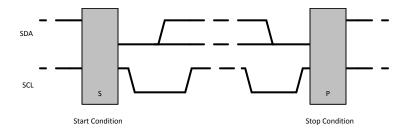

The LM3528 is controlled via an I<sup>2</sup>C-compatible interface. START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as SDA transitioning from HIGH to LOW while SCL is HIGH. A STOP condition is defined as SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. A START and a repeated START conditions are equivalent function-wise. The data on SDA must be stable during the HIGH period of the clock signal (SCL). In other words, the state of SDA can only be changed when SCL is LOW.

Figure 38. Start and Stop Sequences

# I<sup>2</sup>C Compatible Address

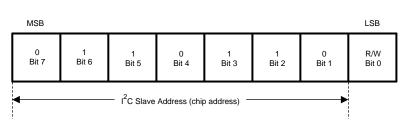

The chip address for the LM3528 is 0110110 (36h). After the START condition, the  $I^2C$  master sends the 7-bit chip address followed by a read or write bit (R/W). R/W= 0 indicates a WRITE and R/W = 1 indicates a READ. The second byte following the chip address selects the register address to which the data will be written. The third byte contains the data for the selected register.

Figure 39. Chip Address

# Transferring Data

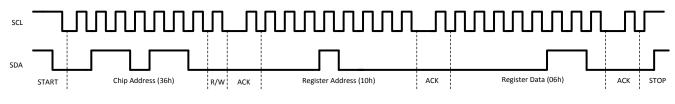

Every byte on the SDA line must be eight bits long, with the most significant bit (MSB) transferred first. Each byte of data must be followed by an acknowledge bit (ACK). The acknowledge related clock pulse (9th clock pulse) is generated by the master. The master releases SDA (HIGH) during the 9th clock pulse. The LM3528 pulls down SDA during the 9th clock pulse, signifying an acknowledge. An acknowledge is generated after each byte has been received. Figure 40 is an example of a write sequence to the General Purpose register of the LM3528.

Figure 40. Write Sequence to the LM3528

# **Register Descriptions**

There are 4, 8 bit registers within the LM3528 as detailed in Table 1.

| Register Name                      | Hex Address | Power -On-Value |

|------------------------------------|-------------|-----------------|

| General Purpose (GP)               | 0x10        | 0xC0            |

| Brightness Main (BMAIN)            | 0xA0        | 0x80            |

| Brightness Sub (BSUB)              | 0xB0        | 0x80            |

| HWEN/PGEN/GPIO Control (HPG)       | 0x80        | 0XF8            |

| General Purpose I/O Control (GPIO) | 0x81        | 0xFC            |

| Pattern Register 0 (PGEN0)         | 0x90        | 0x00            |

| Pattern Register 1 (PGEN1)         | 0x91        | 0x00            |

| Pattern Register 2 (PGEN2)         | 0x92        | 0x00            |

| Pattern Register 3 (PGEN3)         | 0x93        | 0x00            |

Table 1. LM3528 Register Descriptions

# General Purpose Register (GP)

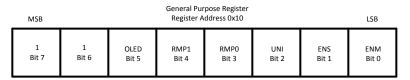

The General Purpose register has four functions. It controls the on/off state of MAIN and SUB/FB, it selects between Unison or Non-Unison mode, provides for control over the rate of change of the LED current (see Brightness Rate of Change Description), and selects between White LED and OLED mode. Figure 41 and Table 2 describes each bit available within the General Purpose Register. Table 3 summarizes the output state of the LM3528 for the different combinations of General Purpose register settings.

### Figure 41. General Purpose Register Description

### Table 2. General Purpose Register Bit Function

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                           | Power-On-<br>Value |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 0   | ENM        | Enable MAIN. Writing a 1 to this bit enables the main current sink (MAIN). Writing a 0 to this bit disables the main current sink and forces MAIN high impedance.                                                                                                                                                                                                                                                                                  | 0                  |

| 1   | ENS        | Enable SUB/FB. Writing a 1 to this bit enables the secondary current sink (SUB/FB). Writing a 0 to this bit disables the secondary current sink and forces SUB/FB high impedance.                                                                                                                                                                                                                                                                  | 0                  |

| 2   | UNI        | Unison Mode Select. Writing a 1 to this bit disables the BSUB register and causes the contents of BMAIN to set the current in both the MAIN and SUB/FB current sinks. Writing a 0 to this bit allows the current into MAIN and SUB/FB to be independently controlled via the BMAIN and BSUB registers respectively.                                                                                                                                | 0                  |

| 3   | RMP0       | Brightness Rate of Change. Bits RMP0 and RMP1 set the rate of change of the LED current into                                                                                                                                                                                                                                                                                                                                                       | 0                  |

| 4   | RMP1       | MAIN and SUB/FB in response to changes in the contents of registers BMAIN and BSUB (see<br>Brightness Rate of Change Description).                                                                                                                                                                                                                                                                                                                 | 0                  |

| 5   | OLED       | OLED = 0 places the LM3528 in White LED mode. In this mode both the MAIN and SUB/FB current sinks are active. The boost converter ensures there is at least 500mV at V <sub>MAIN</sub> and V <sub>SUB/FB</sub> . OLED = 1 places the LM3528 in OLED mode. In this mode the boost converter regulates V <sub>SUB/FB</sub> to 1.244V. V <sub>MAIN</sub> is unregulated and must be > 400mV for the MAIN current sink to maintain current regulation. | 0                  |

| 6   | Don't Care | These are non-functional read only bits. They will always read back as a 1.                                                                                                                                                                                                                                                                                                                                                                        | 1                  |

| 7   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

### Table 3. Operational Truth Table

| UNI | OLED | ENM | ENS | Result                                                                                                                       |

|-----|------|-----|-----|------------------------------------------------------------------------------------------------------------------------------|

| Х   | 0    | 0   | 0   | LM3528 Disabled                                                                                                              |

| 1   | 0    | 1   | Х   | MAIN and SUB/FB current sinks enabled. Current levels set by contents of BMAIN.                                              |

| 1   | 0    | 0   | X   | MAIN and SUB/FB Disabled                                                                                                     |

| 0   | 0    | 0   | 1   | SUB/FB current sink enabled. Current level set by BSUB.                                                                      |

| 0   | 0    | 1   | 0   | MAIN current sink enabled. Current level set by BMAIN.                                                                       |

| 0   | 0    | 1   | 1   | MAIN and SUB/FB current sinks enabled. Current levels set by contents of BMAIN and BSUB respectively.                        |

| x   | 1    | 1   | Х   | SUB/FB current sink disabled (SUB/FB configured as a feedback pin).<br>MAIN current sink enabled current level set by BMAIN. |

| X   | 1    | 0   | Х   | SUB/FB current sink disabled (SUB/FB configured as a feedback pin).<br>MAIN current sink disabled.                           |

\* ENM ,ENS, or OLED high enables analog circuitry.

# **Brightness Registers (BMAIN and BSUB)**

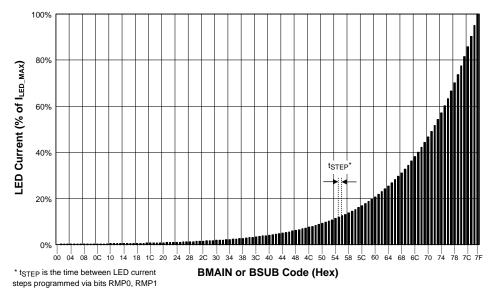

With the UNI bit (General Purpose register) set to 0 (Non-Unison mode) both brightness registers (BMAIN and BSUB) independently control the LED currents  $I_{MAIN}$  and  $I_{SUB/FB}$  respectively. BMAIN and BSUB are both 8 bit, but with only the 7 LSB's controlling the current. The MSB's is a don't care. The LED current control is designed to approximate an exponentially increasing response of the LED current vs increasing code in either BMAIN or BSUB (see Figure 44). Program  $I_{LED}$  MAX by connecting a resistor (RSET) from SET to GND, where:

$$I_{\text{LED}_{\text{MAX}}} = 192 \times \frac{1.244 \text{V}}{\text{R}_{\text{SET}}}$$

Copyright © 2008–2012, Texas Instruments Incorporated

www.ti.com

With the UNI bit (General Purpose register) set to 1 (Unison mode), BSUB is disabled and BMAIN sets both  $I_{MAIN}$  and  $I_{SUB/FB}$ . This prevents the independent control of  $I_{MAIN}$  and  $I_{SUB/FB}$ , however matching between current sinks goes from typically 1%(with UNI = 0) to typically 0.15% (with UNI = 1). Figure 42 and Figure 43 show the register descriptions for the Brightness MAIN and Brightness SUB registers. Table 4 and Figure 44 show  $I_{MAIN}$  and/or  $I_{SUB/FB}$  vs. brightness data as a percentage of  $I_{LED_MAX}$ .

| MSB   | Brightness Main Register<br>Register Address 0xA0 |       |       |       |       |       |       |  |

|-------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| 1     | Data                                              | Data  | Data  | Data  | Data  | Data  | Data  |  |

| Bit 7 | Bit 6                                             | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

| MSB   |       | Brightness Sub Register<br>Register Address 0xB0 |       |       |       |       |       |  |  |

|-------|-------|--------------------------------------------------|-------|-------|-------|-------|-------|--|--|

| 1     | Data  | Data                                             | Data  | Data  | Data  | Data  | Data  |  |  |

| Bit 7 | Bit 6 | Bit 5                                            | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| Figure 43    | Brightness  | SUB | Register | Description |

|--------------|-------------|-----|----------|-------------|

| i igui c to. | Dirginalcoo | 000 | Register | Description |

| BMAIN or<br>BSUB<br>Brightness<br>Data | % of<br>I <sub>LED_MAX</sub> | BMAIN or BSUB<br>Brightness Data | % of I <sub>LED_MAX</sub> | BMAIN or BSUB<br>Brightness Data | % of I <sub>LED_MAX</sub> | BMAIN or<br>BSUB<br>Brightness<br>Data | % of I <sub>LED_MAX</sub> |

|----------------------------------------|------------------------------|----------------------------------|---------------------------|----------------------------------|---------------------------|----------------------------------------|---------------------------|

| 0000000                                | 0.000%                       | 0100000                          | 0.803%                    | 1000000                          | 4.078%                    | 1100000                                | 20.713%                   |

| 0000001                                | 0.166%                       | 0100001                          | 0.845%                    | 1000001                          | 4.290%                    | 1100001                                | 21.792%                   |

| 0000010                                | 0.175%                       | 0100010                          | 0.889%                    | 1000010                          | 4.514%                    | 1100010                                | 22.928%                   |

| 0000011                                | 0.184%                       | 0100011                          | 0.935%                    | 1000011                          | 4.749%                    | 1100011                                | 24.122%                   |

| 0000100                                | 0.194%                       | 0100100                          | 0.984%                    | 1000100                          | 4.996%                    | 1100100                                | 25.379%                   |

| 0000101                                | 0.204%                       | 0100101                          | 1.035%                    | 1000101                          | 5.257%                    | 1100101                                | 26.701%                   |

| 0000110                                | 0.214%                       | 0100110                          | 1.089%                    | 1000110                          | 5.531%                    | 1100110                                | 28.092%                   |

| 0000111                                | 0.226%                       | 0100111                          | 1.146%                    | 1000111                          | 5.819%                    | 1100111                                | 29.556%                   |

| 0001000                                | 0.237%                       | 0101000                          | 1.205%                    | 1001000                          | 6.122%                    | 1101000                                | 31.096%                   |

| 0001001                                | 0.250%                       | 0101001                          | 1.268%                    | 1001001                          | 6.441%                    | 1101001                                | 32.716%                   |

| 0001010                                | 0.263%                       | 0101010                          | 1.334%                    | 1001010                          | 6.776%                    | 1101010                                | 34.420%                   |

| 0001011                                | 0.276%                       | 0101011                          | 1.404%                    | 1001011                          | 7.129%                    | 1101011                                | 36.213%                   |

| 0001100                                | 0.291%                       | 0101100                          | 1.477%                    | 1001100                          | 7.501%                    | 1101100                                | 38.100%                   |

| 0001101                                | 0.306%                       | 0101101                          | 1.554%                    | 1001101                          | 7.892%                    | 1101101                                | 40.085%                   |

| 0001110                                | 0.322%                       | 0101110                          | 1.635%                    | 1001110                          | 8.303%                    | 1101110                                | 42.173%                   |

| 0001111                                | 0.339%                       | 0101111                          | 1.720%                    | 1001111                          | 8.735%                    | 1101111                                | 44.371%                   |

| 0010000                                | 0.356%                       | 0110000                          | 1.809%                    | 1010000                          | 9.191%                    | 1110000                                | 46.682%                   |

| 0010001                                | 0.375%                       | 0110001                          | 1.904%                    | 1010001                          | 9.669%                    | 1110001                                | 49.114%                   |

| 0010010                                | 0.394%                       | 0110010                          | 2.003%                    | 1010010                          | 10.173%                   | 1110010                                | 51.673%                   |

| 0010011                                | 0.415%                       | 0110011                          | 2.107%                    | 1010011                          | 10.703%                   | 1110011                                | 54.365%                   |

| 0010100                                | 0.436%                       | 0110100                          | 2.217%                    | 1010100                          | 11.261%                   | 1110100                                | 57.198%                   |

| 0010101                                | 0.459%                       | 0110101                          | 2.332%                    | 1010101                          | 11.847%                   | 1110101                                | 60.178%                   |

| 0010110                                | 0.483%                       | 0110110                          | 2.454%                    | 1010110                          | 12.465%                   | 1110110                                | 63.313%                   |

| 0010111                                | 0.508%                       | 0111011                          | 2.582%                    | 1010111                          | 13.114%                   | 1110111                                | 66.611%                   |

| 0011000                                | 0.535%                       | 0110111                          | 2.716%                    | 1011000                          | 13.797%                   | 1111000                                | 70.082%                   |

# Table 4. I<sub>LED</sub> vs. Brightness Register Data

#### SNVS513A - AUGUST 2008 - REVISED AUGUST 2012

|                                        | Table 4. ILED VS. Brightness Register Data (continued) |                                  |                           |                                  |                           |                                        |                           |  |  |  |  |  |

|----------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------|----------------------------------|---------------------------|----------------------------------------|---------------------------|--|--|--|--|--|

| BMAIN or<br>BSUB<br>Brightness<br>Data | % of<br>I <sub>LED_MAX</sub>                           | BMAIN or BSUB<br>Brightness Data | % of I <sub>LED_MAX</sub> | BMAIN or BSUB<br>Brightness Data | % of I <sub>LED_MAX</sub> | BMAIN or<br>BSUB<br>Brightness<br>Data | % of I <sub>LED_MAX</sub> |  |  |  |  |  |

| 0011001                                | 0.563%                                                 | 0111000                          | 2.858%                    | 1011001                          | 14.516%                   | 1111001                                | 73.733%                   |  |  |  |  |  |

| 0011010                                | 0.592%                                                 | 0111001                          | 3.007%                    | 1011010                          | 15.272%                   | 1111010                                | 77.574%                   |  |  |  |  |  |

| 0011011                                | 0.623%                                                 | 0111010                          | 3.163%                    | 1011011                          | 16.068%                   | 1111011                                | 81.616%                   |  |  |  |  |  |

| 0011100                                | 0.655%                                                 | 0111011                          | 3.328%                    | 1011100                          | 16.905%                   | 1111100                                | 85.868%                   |  |  |  |  |  |

| 0011101                                | 0.689%                                                 | 0111100                          | 3.502%                    | 1011101                          | 17.786%                   | 1111101                                | 90.341%                   |  |  |  |  |  |

| 0011110                                | 0.725%                                                 | 0111101                          | 3.684%                    | 1011110                          | 18.713%                   | 1111110                                | 95.048%                   |  |  |  |  |  |

| 0011111                                | 0.763%                                                 | 0111111                          | 3.876%                    | 1011111                          | 19.687%                   | 1111111                                | 100.000%                  |  |  |  |  |  |

### Table 4. ILED vs. Brightness Register Data (continued)

Figure 44. I<sub>MAIN</sub> or I<sub>SUB</sub> vs BMAIN or BSUB Data

# **Brightness Rate of Change Description**

RMP0 and RMP1 control the rate of change of the LED current  $I_{MAIN}$  and  $I_{SUB/FB}$  in response to changes in BMAIN and/or BSUB. There are 4 user programmable LED current rates of change settings for the LM3528 (see Table 5).

| Table 5. Rate of Change Bi |

|----------------------------|

|----------------------------|

| RMP0 | RMP1 Change Rate (t <sub>STEP</sub> ) |              |

|------|---------------------------------------|--------------|

| 0    | 0                                     | 12.75µs/step |

| 0    | 1                                     | 3.25ms/step  |

| 1    | 0                                     | 6.5ms/step   |

| 1    | 1                                     | 13ms/step    |

For example, if  $R_{SET} = 12.1 k\Omega$  then  $I_{LED_MAX} = 20mA$ . With the contents of BMAIN set to 0x7F ( $I_{MAIN} = 20mA$ ), suppose the contents of BMAIN are changed to 0x00 resulting in ( $I_{MAIN} = 0mA$ ). With RMP0 =1 and RMP1 = 1 (13ms/step),  $I_{MAIN}$  will change from 20mA to 0mA in 127 steps with 13ms elapsing between steps, excluding the step from 0x7F to 0x7E, resulting in a full scale current change in 1638ms. The total time to transition from one brightness code to another is:

$t_{transition} = (|InitialCode - FinalCode| - 1) \times t_{STEP}$

The following 3 additional examples detail possible scenarios when using the brightness register in conjunction with the rate of change bits and the enable bits.

# Example 1:

Step 1: Write to BMAIN a value corresponding to  $I_{MAIN} = 20$ mA.

Step 2: Write 1 to ENM (turning on MAIN)

Step 3:  $I_{MAIN}$  ramps to 20mA with a rate set by RMP0 and RMP1. (RMP0 and RMP1 bits set the duration spent at one brightness code before incrementing to the next).

Step 4: ENM is set to 0 before 20mA is reached, thus the LED current fades off at a rate given by RMP0 and RMP1 without  $I_{MAIN}$  going up to 20mA.

### Example 2:

Step 1: ENM is 1, and BMAIN has been programmed with code 0x01. This results in a small current into MAIN.

Step 2: BMAIN is programmed with 0x7F (full scale current). This causes  $I_{MAIN}$  to ramp toward full-scale at the rate selected by RMP0 and RMP1.

Step 3: Before I<sub>MAIN</sub> reaches full-scale BMAIN is programmed with 0x30. I<sub>MAIN</sub> will continue to ramp to full scale.

Step 4: When  $I_{MAIN}$  has reached full-scale value it will ramp down to the current corresponding to 0x30 at a rate set by RMP0 and RMP1.

### Example 3:

Step 1: Write to BMAIN a value corresponding to  $I_{MAIN} = 20$ mA.

Step 2: Write a 1 to both RMP0 and RMP1.

Step 3: Write 1 to ENM (turning on MAIN).

Step 4: I<sub>MAIN</sub> ramps toward 20mA with a rate set by RMP0 and RMP1. (RMP0 and RMP1 bits set the duration spent at one brightness code before incrementing to the next).

Step 5: After 1.222s I<sub>MAIN</sub> has ramped to 19.687% of I<sub>LED\_MAX</sub> (0.19687 × 20mA = 3.9374mA). Simultaneously, RMP0 and RMP1 are both programmed with 0.

Step 6: I<sub>MAIN</sub> continues ramping from 3.9374mA to 20mA, but at a new ramp rate of 12.75µs/step.

#### SNVS513A - AUGUST 2008 - REVISED AUGUST 2012

|                                                                                                                                                                                                                            | Table 6. HPG Register Function                                     |                         |                                   |                            |                                                                                                                                                              |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|-----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bits 7 – 6<br>(PGEN Bit<br>Period)                                                                                                                                                                                         | Bits 5 - 3 (PGEN<br>Enable/Disable and<br>Duty Cycle<br>Selection) | Bit 2<br>(GPIO<br>Data) | Bit 1 (GPIO<br>Data<br>Direction) | Bit 0<br>(HWEN<br>Control) | Function                                                                                                                                                     |  |  |  |  |  |  |

| X                                                                                                                                                                                                                          | Х                                                                  | Х                       | Х                                 | 0                          | HWEN/PGEN/GPIO is configured as an active high<br>Hardware Enable Input (HWEN)                                                                               |  |  |  |  |  |  |

| $\begin{array}{l} 00 &= 1.6 \mu \text{s/bit} \\ (625 \text{kHz}) \\ 01 &= 26 \text{ms/bit} \\ (38 \text{Hz}) \\ 10 &= 52 \text{ms/bit} \\ (19 \text{Hz}) \\ 11 &= 105 \text{ms/bit} \\ (9.5 \text{Hz}) \\ (1) \end{array}$ | 010 = 1/2<br>011 = 1/3<br>100 = 1/4<br>101 = 1/6<br>110 = 1/6      | x                       | X                                 | 1                          | HWEN/PGEN/GPIO is configured as a Pattern Generator<br>Output with the frequency set by bits <7:6> and the duty<br>cycle set by bits <5:3>. (See Figure 46.) |  |  |  |  |  |  |

| X                                                                                                                                                                                                                          | 000                                                                | GPIO<br>Read Data       | 1                                 | 1                          | HWEN/PGEN/GPIO is configured as a GPIO Input. Read data from bit 2.                                                                                          |  |  |  |  |  |  |

| X                                                                                                                                                                                                                          | 000                                                                | GPIO<br>Write Data      | 0                                 | 1                          | HWEN/PGEN/GPIO is configured as a GPIO Output. A '1' written to bit 2 will force HWEN/PGEN/GPIO high; a 0 written to bit 2 will force HWEN/PGEN/GPIO low.    |  |  |  |  |  |  |

(1) This represents the amount of time each programmed bit will be present at HWEN/PGEN/GPIO. The entire pattern period will be 32 × Bit Period.

(2) This duty cycle indicates the fraction of time the pattern is being output at HWEN/PGEN/GPIO. For example the 1/2 duty cycle (bits <5:3> = 010) will have the 32 bit pattern output once followed by a dead time (HWEN/PGEN/GPIO high impedance) equal to 1x's the pattern period (Deadtime = 32 x Bit\_Period x (1/DutyCycle -1). For the 100% duty cycle setting the 32 bit pattern will repeat constantly with no deadtime.

| MSB                             |                                 |                                  | Register A                       | NGPIO Register<br>ddress 0x80<br>Reset = 0x01 |                       |                                    | LSB                                 |

|---------------------------------|---------------------------------|----------------------------------|----------------------------------|-----------------------------------------------|-----------------------|------------------------------------|-------------------------------------|

| Frequency<br>Selection<br>Bit 7 | Frequency<br>Selection<br>Bit 6 | Duty Cycle<br>Selection<br>Bit 5 | Duty Cycle<br>Selection<br>Bit 4 | Duty Cycle<br>Selection<br>Bit 3              | GPIO<br>Data<br>Bit 2 | GPIO<br>Data<br>Direction<br>Bit 1 | HWEN<br>Enable/<br>Disable<br>Bit 0 |

# Figure 45. HPG Register Description

| Bits 7 - 2 | GPIO Data (Bit 1) | Data Direction (Bit 0) | Function                                                                                                                   |

|------------|-------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------|

| x          | x                 | 0                      | GPIO is configured as a GPIO<br>input with the input data read<br>back via bit [1]. This is the default<br>power on state. |

| X          | X                 | 1                      | GPIO is configured as a logic<br>output. The output logic voltage<br>is written to bit [1].                                |

### Table 7. GPIO Register Function

| MSB        | GPIO Register<br>Register Address 0x81<br>Power On Reset = 0xFC |            |            |            |            |               |                            |  |  |  |

|------------|-----------------------------------------------------------------|------------|------------|------------|------------|---------------|----------------------------|--|--|--|

| 1<br>Bit 7 | 1<br>Bit 6                                                      | 1<br>Bit 5 | 1<br>Bit 4 | 1<br>Bit 3 | 1<br>Bit 2 | Data<br>Bit 1 | Data<br>Direction<br>Bit 0 |  |  |  |

# Figure 46. GPIO Register Description

Figure 47 – Figure 50 detail the Pattern Generator Data Registers. These hold the 32 bit data that is output at HWEN/PGEN/GPIO in PGEN mode. The data is output LSB first (Bit 0 of PGEN0) and MSB last (Bit 7 of PGEN3).

TEXAS INSTRUMENTS

# SNVS513A - AUGUST 2008 - REVISED AUGUST 2012

www.ti.com

| MSB    | PGEN0 Register<br>Register Address 0x90<br>B Power On Reset = 0x00 |        |        |        |        |        |        |  |  |  |

|--------|--------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| PGEN   | PGEN                                                               | PGEN   | PGEN   | PGEN   | PGEN   | PGEN   | PGEN   |  |  |  |

| DATA 7 | DATA 6                                                             | DATA 5 | DATA 4 | DATA 3 | DATA 2 | DATA 1 | DATA 0 |  |  |  |

| Bit 7  | Bit 6                                                              | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |  |  |  |

### Figure 47. PGEN0 Register Description

| MSB     |         |         | Register A | Register<br>ddress 0x91<br>Reset = 0x00 |         |        | LSB    |

|---------|---------|---------|------------|-----------------------------------------|---------|--------|--------|

| PGEN    | PGEN    | PGEN    | PGEN       | PGEN                                    | PGEN    | PGEN   | PGEN   |

| DATA 15 | DATA 14 | DATA 13 | DATA 12    | DATA 11                                 | DATA 10 | DATA 9 | DATA 8 |

| Bit 7   | Bit 6   | Bit 5   | Bit 4      | Bit 3                                   | Bit 2   | Bit 1  | Bit 0  |

| MSB     |         | PGEN2 Register<br>Register Address 0x92<br>Power On Reset = 0x00 |         |         |         |         |         |  |  |  |  |

|---------|---------|------------------------------------------------------------------|---------|---------|---------|---------|---------|--|--|--|--|

| PGEN    | PGEN    | PGEN                                                             | PGEN    | PGEN    | PGEN    | PGEN    | PGEN    |  |  |  |  |

| DATA 23 | DATA 22 | DATA 21                                                          | DATA 20 | DATA 19 | DATA 18 | DATA 17 | DATA 16 |  |  |  |  |

| Bit 7   | Bit 6   | Bit 5                                                            | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |  |  |  |

| MSB     | PGEN3 Register<br>Register Address 0x93<br>ISB Power On Reset = 0x00 |         |         |         |         |         |         |  |  |

|---------|----------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|--|--|

| PGEN    | PGEN                                                                 | PGEN    | PGEN    | PGEN    | PGEN    | PGEN    | PGEN    |  |  |

| DATA 31 | DATA 30                                                              | DATA 29 | DATA 28 | DATA 27 | DATA 26 | DATA 25 | DATA 24 |  |  |

| Bit 7   | Bit 6                                                                | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |  |

Figure 50. PGEN3 Register Description

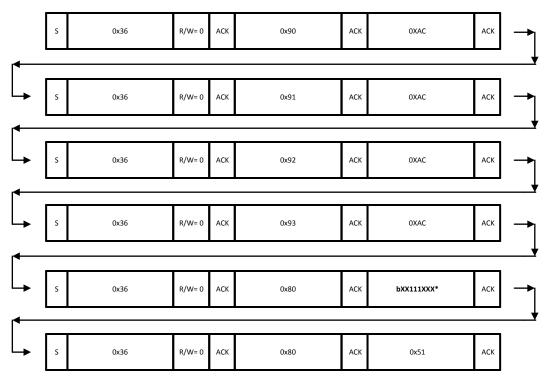

Figure 51 shows a write sequence to the pattern generator programmed to output the waveform in Figure 52. In this example HPG register bits <7:6> = 01 (for 26ms/bit) and bits <5:3> = 010 (for 1/2 duty cycle). The pattern data in registers (PGEN0 – PGEN2) are all loaded with 0xAC. A '1' will force the HWEN/PGEN/GPIO output low while a '0' will force HWEN/PGEN/GPIO open drain. When set for a 26ms/bit period the pattern will be output LSB first (PGEN0, bit 0) and repeat every

$$t_{\text{PERIOD}} = \frac{26 \text{ ms/bit} \times 32 \text{ bits}}{1/2 \text{ Dutycycle}} = 1.664 \text{s}$$

(4)

When set for ½ duty cycle there will be a dead time (HWEN/PGEN/GPIO high impedance) between each pattern and equal to the pattern period. In applications where HWEN/PGEN/GPIO is used to pull current through an indicator LED a '1' corresponds to the LED on and a '0' corresponds to the LED off.

**EXAS**

NSTRUMENTS

SNVS513A - AUGUST 2008 - REVISED AUGUST 2012

\*Only bits <5:3> are necessary in this byte the rest are don't cares. Bits <5:3> = '111' are necessary to latch the pattern generator data bits into the internal shift register.

### Figure 51. Pattern Generation Write Sequence

# Shutdown and Output Isolation

The LM3528 provides a true shutdown for either MAIN or SUB/FB when configured as a White LED bias supply. Write a 0 to ENM (bit 1) of the General Purpose register to turn off the MAIN current sink and force MAIN high impedance. Write a 0 to ENS (bit 2) of the General Purpose register to turn off the SUB/FB current sink and force SUB/FB high impedance. Writing a 1 to ENM or ENS turns on the MAIN and SUB/FB current sinks respectively. When in shutdown the leakage current into MAIN or SUB/FB is typically 1.8µA. See Typical Performance Characteristics Plots for start-up responses of the LM3528 using the ENM and ENS bits in White LED and OLED modes.

# **Application Information**

### LED Current Setting/Maximum LED Current

Connect a resistor ( $R_{SET}$ ) from SET to GND to program the maximum LED current ( $I_{LED_MAX}$ ) into MAIN or SUB/FB. The  $R_{SET}$  to  $I_{LED_MAX}$  relationship is:

www.ti.com

(5)

**ISTRUMENTS**

FXAS

$$I_{\text{LED}_{\text{MAX}}} = 192 \times \frac{1.244V}{R_{\text{SET}}}$$

where SET provides the constant 1.244V output.

# **Output Voltage Setting (OLED Mode)**

Connect Feedback resistors from the converters output to SUB/FB to GND to set the output voltage in OLED mode (see R1 and R2 in the Figure 1 (OLED Panel Power Supply). First select R2 <  $100k\Omega$  then calculate R1 such that:

$$R1 = R2 \left( \frac{V_{OUT}}{1.21V} - 1 \right)$$

(6)

In OLED mode the MAIN current sink continues to regulate the current through MAIN, however,  $V_{MAIN}$  is no longer regulated. To avoid dropout and ensure proper current regulation the application must ensure that  $V_{MAIN} > 0.3V$ .

### Input Capacitor Selection

Choosing the correct size and type of input capacitor helps minimize the input voltage ripple caused by the switching of the LM3528's boost converter. For continuous inductor current operation the input voltage ripple is composed of 2 primary components, the capacitor discharge (delta  $V_Q$ ) and the capacitor's equivalent series resistance (delta  $V_{ESR}$ ). These ripple components are found by:

$$\Delta V_{Q} = \frac{\Delta I_{L} \times D}{2 \times f_{SW} \times C_{IN}}$$

and

$$\Delta V_{ESR} = 2 \times \Delta I_{L} \times R_{ESR}$$

ere

$$\Delta I_{L} = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{2 \times f_{SW} \times L \times V_{OUT}}$$

(7)

In the typical application circuit a  $1\mu$ F ceramic input capacitor works well. Since the ESR in ceramic capacitors is typically less than  $5m\Omega$  and the capacitance value is usually small, the input voltage ripple is primarily due to the capacitive discharge. With larger value capacitors such as tantalum or aluminum electrolytic the ESR can be greater than  $0.5\Omega$ . In this case the input ripple will primarily be due to the ESR.

### **Output Capacitor Selection**

wh

The LM3528's output capacitor supplies the LED current during the boost converters on time. When the switch turns off the inductor energy is discharged through the diode supplying power to the LED's and restoring charge to the output capacitor. This causes a sag in the output voltage during the on time and a rise in the output voltage during the off time. The output capacitor is therefore chosen to limit the output ripple to an acceptable level depending on LED or OLED panel current requirements and input/output voltage differentials. For proper operation ceramic output capacitors ranging from  $1\mu$ F to  $2.2\mu$ F are required.

As with the input capacitor, the output voltage ripple is composed of two parts, the ripple due to capacitor discharge (delta  $V_Q$ ) and the ripple due to the capacitors ESR (delta  $V_{ESR}$ ). For continuous conduction mode, the ripple components are found by:

$$\Delta V_{Q} = \frac{I_{LED} \times (V_{OUT} - V_{IN})}{f_{SW} \times V_{OUT} \times C_{OUT}} \text{ and}$$

$$\Delta V_{ESR} = R_{ESR} \times \left(\frac{I_{LED} \times V_{OUT}}{V_{IN}} + \Delta I_{L}\right)$$

where

$$\Delta I_{L} = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{2 \times f_{SW} \times L \times V_{OUT}}$$

#### www.ti.com