# LM4936 Boomer<sup>™</sup> Audio Power Amplifier Series Stereo 2W Audio Power Amplifiers with Volume Control and Selectable Control Interface (SPI or I<sup>2</sup>C)

Check for Samples: LM4936

#### **FEATURES**

- Selectable SPI or I<sup>2</sup>C Control Interface

- System Beep Detect

- Stereo Switchable Bridged/Single-Ended Power Amplifiers

- Selectable Internal/External Gain and Bass Boost

- "Click and Pop" Suppression Circuitry

- Thermal Shutdown Protection Circuitry

- Headphone Sense

#### **APPLICATIONS**

- Portable and Desktop Computers

- Multimedia Monitors

- Portable Radios, PDAs, and Portable TVs

#### **KEY SPECIFICATIONS**

- P<sub>O</sub> at 1% THD+N

- into  $3\Omega$ , 2.2W (Typ)

- into  $4\Omega$ , 2.0W (Typ)

- into 8Ω, 1.25W (Typ)

- Single-ended mode THD+N at 90mW into 32Ω, 1% (Typ)

- Shutdown current, 0.7μA (Typ)

#### DESCRIPTION

The LM4936 is a monolithic integrated circuit that provides volume control, and stereo bridged audio power amplifiers capable of producing 2W into 4 $\Omega$  <sup>(1)</sup> with less than 1% THD or 2.2W into 3 $\Omega$  <sup>(2)</sup> with less than 1% THD.

Boomer audio integrated circuits were designed specifically to provide high quality audio while requiring a minimum amount of external components. The LM4936 incorporates a SPI or I<sup>2</sup>C Control Interface that runs the volume control, stereo bridged audio power amplifiers and a selectable gain or bass boost. All of the LM4936's features (i.e. SD, Mode, Mute, Gain Sel) make it optimally suited for multimedia monitors, portable radios, desktop, and portable computer applications.

The LM4936 features an externally controlled, low-power consumption shutdown mode, and both a power amplifier and headphone mute for maximum system flexibility and performance.

- (1) When properly mounted to the circuit board, LM4936MH will deliver 2W into 4Ω. See Application Information section HTSSOP PACKAGE PCB MOUNTING CONSIDERATIONS for more information.

- (2) An LM4936MH that has been properly mounted to the circuit board and forced-air cooled will deliver 2.2W into  $3\Omega$ .

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Boomer is a trademark of Texas Instruments.

SNAS269 – APRIL 2005

www.ti.com

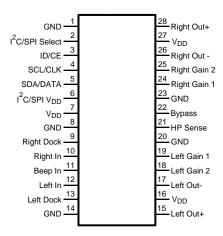

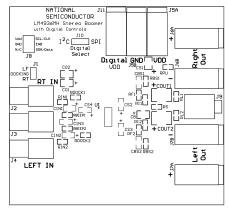

## **Connection Diagram**

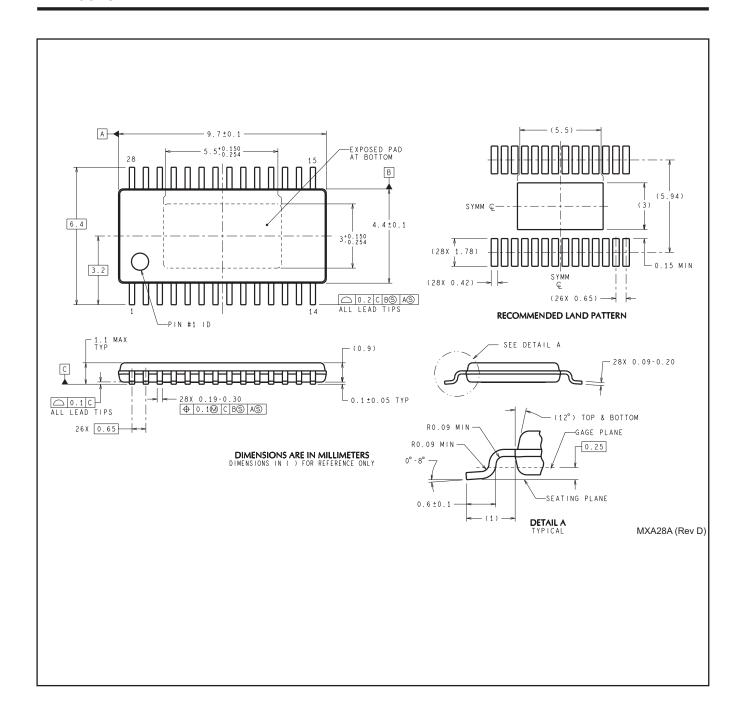

Figure 1. HTSSOP Package (Top View) See Package Number PWP0028A for HTSSOP

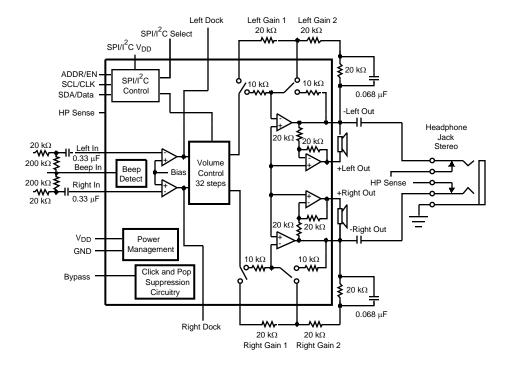

# **Block Diagram**

Figure 2. LM4936 Block Diagram

Submit Documentation Feedback

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)

| / too o to |                                                          |                       |                                |  |

|------------------------------------------|----------------------------------------------------------|-----------------------|--------------------------------|--|

| Supply Voltage                           |                                                          |                       | 6.0V                           |  |

| Storage Temperature                      |                                                          |                       | -65°C to +150°C                |  |

| Input Voltage                            |                                                          |                       | -0.3V to V <sub>DD</sub> +0.3V |  |

| Power Dissipation (3)                    | Internally limited                                       |                       |                                |  |

| ESD Susceptibility (4)                   | 2000V                                                    |                       |                                |  |

| ESD Susceptibility <sup>(5)</sup>        | 200V                                                     |                       |                                |  |

| Junction Temperature                     |                                                          |                       | 150°C                          |  |

| Caldarina lafarrastica                   | Carall Outline Basks as                                  | Vapor Phase (60 sec.) | 215°C                          |  |

| Soldering Information                    | Small Outline Package                                    | Infrared (15 sec.)    | 220°C                          |  |

| θ <sub>JC</sub> (typ) - PWP0028A         |                                                          |                       | 2°C/W                          |  |

| θ <sub>JA</sub> (typ) - PWP0028A (H      | TSSOP) <sup>(6)</sup>                                    |                       | 41°C/W                         |  |

| θ <sub>JA</sub> (typ) - PWP0028A (H      | 54°C/W                                                   |                       |                                |  |

| θ <sub>JA</sub> (typ) - PWP0028A (H      | θ <sub>JA</sub> (typ) - PWP0028A (HTSSOP) <sup>(8)</sup> |                       |                                |  |

| θ <sub>JA</sub> (typ) - PWP0028A (H      | TSSOP) <sup>(9)</sup>                                    |                       | 93°C/W                         |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not specified for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (3) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ <sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/θ<sub>JA</sub>. For the LM4936, T<sub>JMAX</sub> = 150°C, and the typical junction-to-ambient thermal resistance for each package can be found in the **Absolute Maximum Ratings** section above.

- (4) Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

- (5) Machine Model, 220pF 240pF discharged through all pins.

- (6) The θ<sub>JA</sub> given is for an PWP0028A package whose HTSSOP is soldered to a 2in² piece of 1 ounce printed circuit board copper on a bottom side layer through 21 8mil vias.

- (7) The θ<sub>JA</sub> given is for an PWP0028A package whose HTSSOP is soldered to an exposed 2in <sup>2</sup> piece of 1 ounce printed circuit board copper.

- (8) The θ<sub>JA</sub> given is for an PWP0028A package whose HTSSOP is soldered to an exposed 1 in <sup>2</sup> piece of 1 ounce printed circuit board copper.

- (9) The  $\theta_{JA}$  given is for an PWP0028A package whose HTSSOP is not soldered to any copper.

#### Operating Ratings

| - 1                           |                               |                                                    |

|-------------------------------|-------------------------------|----------------------------------------------------|

| Temperature Range             | $T_{MIN} \le T_A \le T_{MAX}$ | -40°C ≤ TA ≤ 85°C                                  |

|                               |                               | 2.7V ≤ V <sub>DD</sub> ≤ 5.5V                      |

| Supply Voltage <sup>(1)</sup> |                               | $I^2C/SPIV_{DD} \le V_{DD}$                        |

|                               |                               | 2.4V ≤ I <sup>2</sup> C/SPI V <sub>DD</sub> ≤ 5.5V |

I<sup>2</sup>C/SPI V<sub>DD</sub> must not be larger than V<sub>DD</sub> at any time or damage to the IC may occur. During power up and power down, I<sup>2</sup>C/SPI V<sub>DD</sub> must remain equal to V<sub>DD</sub> or lower.

Product Folder Links: LM4936

# Electrical Characteristics for Entire IC(1)(2)

The following specifications apply for  $V_{DD} = 5V$  unless otherwise noted. Limits apply for  $T_A = 25$ °C.

| Symbol          | Parameter                          | 0 1111                                | LM                     | Units                |          |

|-----------------|------------------------------------|---------------------------------------|------------------------|----------------------|----------|

|                 |                                    | Conditions                            | Typical <sup>(3)</sup> | Limit <sup>(4)</sup> | (Limits) |

| $V_{DD}$        | Supply Voltage                     |                                       |                        | 2.7                  | V (min)  |

|                 |                                    |                                       |                        | 5.5                  | V (max)  |

| I <sub>DD</sub> | Quiescent Power Supply Current     | $V_{IN} = 0V$ , $I_O = 0A$            | 10                     | 25                   | mA (max) |

| I <sub>SD</sub> | Shutdown Current                   | $V_{\text{shutdown}} = V_{\text{DD}}$ | 0.7                    | 2.0                  | μA (max) |

| V <sub>IH</sub> | Headphone Sense High Input Voltage |                                       |                        | 4                    | V (min)  |

| V <sub>IL</sub> | Headphone Sense Low Input Voltage  |                                       |                        | 0.8                  | V (max)  |

- (1) All voltages are measured with respect to the ground pins, unless otherwise specified. All specifications are tested using the typical application as shown in Figure 2.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not specified for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) Typicals are measured at 25°C and represent the parametric norm.

- (4) Limits are specified to Texas Instruments' AOQL (Average Outgoing Quality Level). Datasheet min/max specification limits are specified by design, test, or statistical analysis.

# Electrical Characteristics for Volume Control (1)(2)

The following specifications apply for  $V_{DD}$  = 5V. Limits apply for  $T_A$  = 25°C.

| Complead           | B                                | Conditions             | LM                     | LM4936               |          |  |

|--------------------|----------------------------------|------------------------|------------------------|----------------------|----------|--|

| Symbol Parameter   |                                  | Conditions             | Typical <sup>(3)</sup> | Limit <sup>(4)</sup> | (Limits) |  |

| C <sub>RANGE</sub> | Volume Control Range             | Maximum gain setting   | 0                      | ±0.75                | dB (max) |  |

|                    |                                  | Minimum gain setting   | -91                    | -75                  | dB (min) |  |

| A <sub>Ch-Ch</sub> | Channel to Channel Gain Mismatch | f <sub>IN</sub> = 1kHz | 0.35                   |                      | dB       |  |

| A <sub>M</sub>     | Mute Attenuation                 | Mute Mode              |                        | -78                  | dB (min) |  |

- (1) All voltages are measured with respect to the ground pins, unless otherwise specified. All specifications are tested using the typical application as shown in Figure 2.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not specified for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) Typicals are measured at 25°C and represent the parametric norm.

- (4) Limits are specified to Texas Instruments' AOQL (Average Outgoing Quality Level). Datasheet min/max specification limits are specified by design, test, or statistical analysis.

Submit Documentation Feedback

Copyright © 2005, Texas Instruments Incorporated

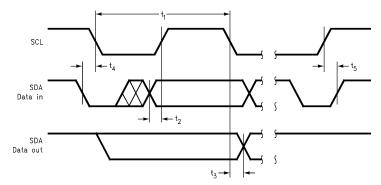

# Electrical Characteristics for Control Interface (1) (2)

The following specifications apply for  $V_{DD}$  = 5V,  $V_{DD}$  = 3V and 2.4V  $\leq$  I<sup>2</sup>C/SPI  $V_{DD}$   $\leq$  5.5V. Limits apply for  $T_A$  = 25°C.

| 0                | B                          | Conditions | LM          | Units                                        |           |

|------------------|----------------------------|------------|-------------|----------------------------------------------|-----------|

| Symbol           | Parameter                  |            | Typical (3) | Limit <sup>(4)</sup>                         | (Limits)  |

| t <sub>1</sub>   | SCL period                 |            |             | 2.5                                          | μs (min)  |

| t <sub>2</sub>   | SDA Set-up Time            |            |             | 100                                          | ns (min)  |

| t <sub>3</sub>   | SDA Stable Time            |            |             | 0                                            | ns (min)  |

| t <sub>4</sub>   | Start Condition Time       |            |             | 100                                          | ns (min)  |

| t <sub>5</sub>   | Stop Condition Time        |            |             | 100                                          | ns (min)  |

| V <sub>IH</sub>  | Digital Input High Voltage |            |             | 0.7 X<br>I <sup>2</sup> C/SPIV <sub>DD</sub> | V (min)   |

| V <sub>IL</sub>  | Digital Input Low Voltage  |            |             | 0.3 X<br>I <sup>2</sup> C/SPIV <sub>DD</sub> | V (max)   |

| t <sub>ES</sub>  | SPI ENABLE Setup Time      |            |             | 50                                           | ns (min)  |

| t <sub>EH</sub>  | SPI ENABLE Hold Time       |            |             | 50                                           | ns (min)  |

| t <sub>EL</sub>  | SPI ENABLE High Time       |            |             | 50                                           | ns (min)  |

| t <sub>DS</sub>  | SPI DATA Setup Time        |            |             | 50                                           | ns (min)  |

| t <sub>DH</sub>  | SPI DATA HOLD Time         |            |             | 50                                           | ns (min)  |

| t <sub>CS</sub>  | SPI CLOCK Setup Time       |            |             | 50                                           | ns (min)  |

| t <sub>CH</sub>  | SPI CLOCK High Pulse Width |            |             | 100                                          | ns (min)  |

| t <sub>CL</sub>  | SPI CLOCK Low Pulse Width  |            |             | 100                                          | ns (min)  |

| f <sub>CLK</sub> | SPI CLOCK Frequency        |            |             | 5                                            | MHz (max) |

- (1) All voltages are measured with respect to the ground pins, unless otherwise specified. All specifications are tested using the typical application as shown in Figure 2.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not specified for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) Typicals are measured at 25°C and represent the parametric norm.

- (4) Limits are specified to Texas Instruments' AOQL (Average Outgoing Quality Level). Datasheet min/max specification limits are specified by design, test, or statistical analysis.

# Electrical Characteristics for Single-Ended Mode Operation (1)(2)

The following specifications apply for  $V_{DD} = 5V$ . Limits apply for  $T_A = 25$ °C.

| 0                 |                                   | 0 111                                                                          | LM4                    | LM4936               |          |  |

|-------------------|-----------------------------------|--------------------------------------------------------------------------------|------------------------|----------------------|----------|--|

| Symbol            | Parameter                         | Conditions                                                                     | Typical <sup>(3)</sup> | Limit <sup>(4)</sup> | (Limits) |  |

| Po                | Output Power                      | THD = 1%; f = 1kHz; $R_L = 32\Omega$                                           | 90                     |                      | mW       |  |

|                   |                                   | THD = 10%; f = 1 kHz; $R_L = 32\Omega$                                         | 110                    |                      | mW       |  |

| THD+N             | Total Harmonic Distortion+Noise   | $P_{OUT}$ = 20mW, f = 1kHz, $R_L$ = 32 $\Omega$ , $A_{VD}$ = 1, 80kHz BW       | 0.02                   |                      | %        |  |

| PSRR              | Power Supply Rejection Ratio      | $C_B = 1\mu F$ , $f = 120Hz$ ,<br>Input Terminated<br>$V_{RIPPLE} = 200mVp$ -p | 57                     |                      | dB       |  |

| N <sub>OUT</sub>  | Output Noise                      | A-Wtd Filter                                                                   | 18                     |                      | μV       |  |

| X <sub>talk</sub> | Channel Separation <sup>(5)</sup> | $f = 1kHz$ , $C_B = 1\mu F$                                                    | 63                     |                      | dB       |  |

- (1) All voltages are measured with respect to the ground pins, unless otherwise specified. All specifications are tested using the typical application as shown in Figure 2.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not specified for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) Typicals are measured at 25°C and represent the parametric norm.

- (4) Limits are specified to Texas Instruments' AOQL (Average Outgoing Quality Level). Datasheet min/max specification limits are specified by design, test, or statistical analysis.

- (5) PCB design will affect Crosstalk performance.

Product Folder Links: LM4936

# Electrical Characteristics for Bridged Mode Operation (1)(2)

The following specifications apply for  $V_{DD} = 5V$ , unless otherwise noted. Limits apply for  $T_A = 25$ °C.

|                   |                                   | 0 1111                                                                                     | LM4936                 |                      | Units    |

|-------------------|-----------------------------------|--------------------------------------------------------------------------------------------|------------------------|----------------------|----------|

| Symbol            | Parameter                         | Conditions                                                                                 | Typical <sup>(3)</sup> | Limit <sup>(4)</sup> | (Limits) |

| Vos               | Output Offset Voltage             | V <sub>IN</sub> = 0V, No Load                                                              | 10                     | 50                   | mV (max) |

| Po                | Output Power                      | THD + N = 1%; f = 1kHz; $R_L = 3\Omega^{(5)}$                                              | 2.2                    |                      | W        |

|                   |                                   | THD + N = 1%; f = 1kHz; $R_L = 4\Omega^{(6)}$                                              | 2                      |                      | W        |

|                   |                                   | THD+N = 1% (max); f = 1kHz; $R_L = 8\Omega$                                                | 1.25                   | 1.0                  | W (min)  |

|                   |                                   | THD+N = 10%; f = 1kHz; $R_L = 8Ω$                                                          | 1.6                    |                      | W        |

| THD+N             | Total Harmonic Distortion+Noise   | $P_O = 0.4W$ , $f = 1kHz$<br>$R_L = 8\Omega$ , $A_{VD} = 2$ , $80kHz$ BW                   | 0.06                   |                      | %        |

| PSRR              | Power Supply Rejection Ratio      | $C_B = 1\mu F, f = 120 Hz,$<br>Input Terminated<br>$V_{RIPPLE} = 200 mVp-p; R_L = 8\Omega$ | 55                     |                      | dB       |

| N <sub>OUT</sub>  | Output Noise                      | A-Wtd Filter                                                                               | 36                     |                      | μV       |

| X <sub>talk</sub> | Channel Separation <sup>(7)</sup> | $f = 1kHz$ , $C_B = 1\mu F$                                                                | 63                     |                      | dB       |

- (1) All voltages are measured with respect to the ground pins, unless otherwise specified. All specifications are tested using the typical application as shown in Figure 2.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not specified for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) Typicals are measured at 25°C and represent the parametric norm.

- (4) Limits are specified to Texas Instruments' AOQL (Average Outgoing Quality Level). Datasheet min/max specification limits are specified by design, test, or statistical analysis.

- (5) When driving 3Ω loads from a 5V supply the LM4936MH must be mounted to the circuit board and forced-air cooled. The demo board shown in the datasheet has planes for heat sinking. The top layer plane is 1.05 in² (675mm²), the inner two layers each have a 1.03 in² (667mm²) plane and the bottom layer has a 3.32 in² (2143mm²) plane. The planes are electrically GND and interconnected through six 15 mil vias directly under the package and eight 28 mil vias in various locations.

- (6) When driving 4Ω loads from a 5V supply the LM4936MH must be mounted to the circuit board. The demo board shown in the datasheet has planes for heat sinking. The top layer plane is 1.05 in² (675mm²), the inner two layers each have a 1.03 in² (667mm²) plane and the bottom layer has a 3.32 in² (2143mm²) plane. The planes are electrically GND and interconnected through six 15 mil vias directly under the package and eight 28 mil vias in various locations.

- (7) PCB design will affect Crosstalk performance.

Submit Documentation Feedback

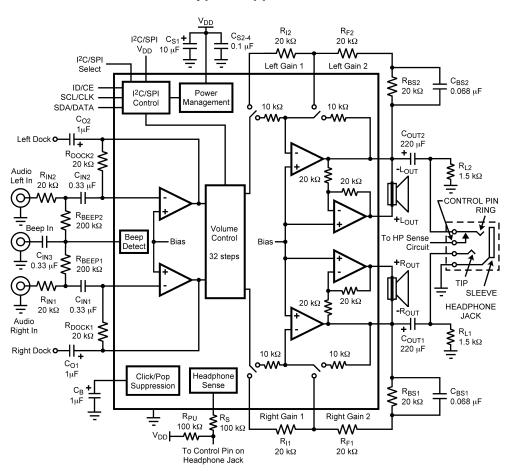

# **Typical Application**

Figure 3. Typical Application Circuit

# Table 1. I<sup>2</sup>C/SPI Interface Controls<sup>(1)</sup>

|                                                   | B7 | В6 | B5 | B4            | В3       | B2   | B1   | В0       |

|---------------------------------------------------|----|----|----|---------------|----------|------|------|----------|

| I <sup>2</sup> C<br>Address                       | 1  | 1  | 0  | 1             | 1        | 0    | ID   | 0        |

| Mode<br>Control<br>Register                       | 0  | 0  | 0  | HP<br>Control | Gain Sel | Mode | Mute | Shutdown |

| Volume<br>Control<br>Register<br>(See Table<br>4) | 1  | 0  | 0  | V4            | V3       | V2   | V1   | Vo       |

<sup>(1)</sup> If system beep is detected on the Beep In pin, the system beep will be passed through the bridged amplifier regardless of the logic of the Mute and HP Control bits (B1, B4) and HP Sense pin.

## **Table 2. Headphone Control**

| HP Sense Pin         | I <sup>2</sup> C/SPI HP Control (B4) | Output Stage Configuration |

|----------------------|--------------------------------------|----------------------------|

| 0                    | 0                                    | BTL                        |

| 0                    | 1                                    | SE                         |

| 1 (V <sub>DD</sub> ) | 0                                    | SE                         |

| 1 (V <sub>DD</sub> ) | 1                                    | SE                         |

# **Table 3. Logic Controls**

| Logic Level | ogic Level B3 (Gain Sel) B2 (Mode) B1 ( |                   | B1 (Mute)       | B0 (Shutdown)   | I <sup>2</sup> C/SPI Select |  |

|-------------|-----------------------------------------|-------------------|-----------------|-----------------|-----------------------------|--|

| 0           | Internal Gain                           | Fixed Volume, 0dB | Mute Off (Play) | Device Shutdown | I <sup>2</sup> C mode       |  |

| 1           | External Gain                           | Adjustable Volume | Mute On         | Device Active   | SPI mode                    |  |

Submit Documentation Feedback

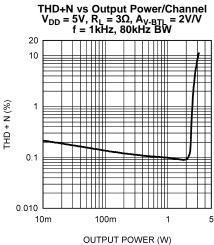

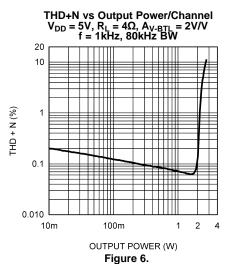

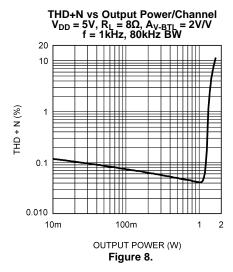

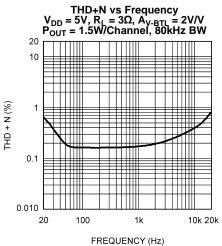

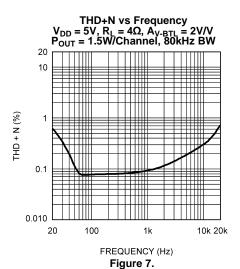

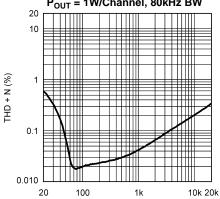

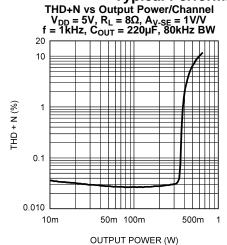

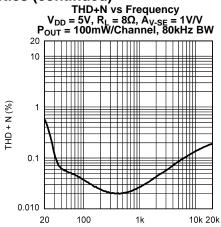

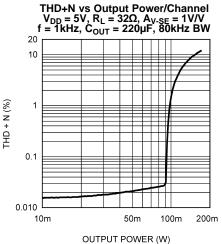

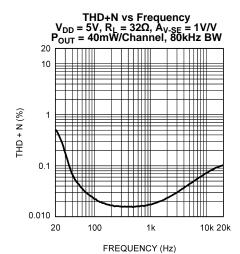

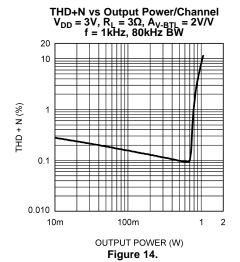

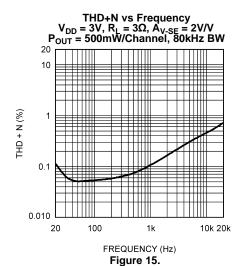

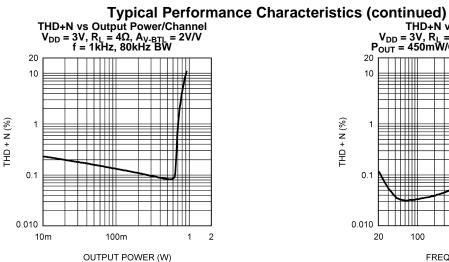

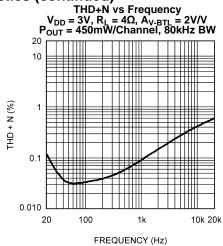

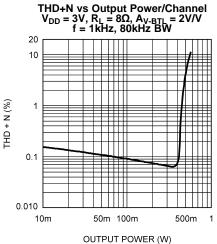

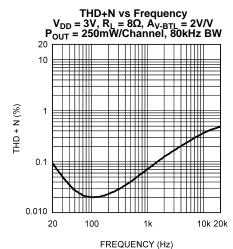

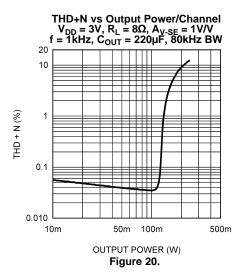

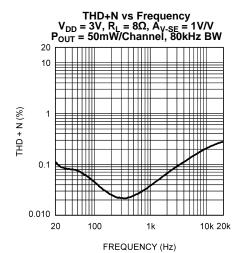

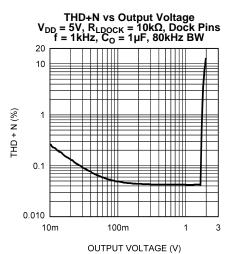

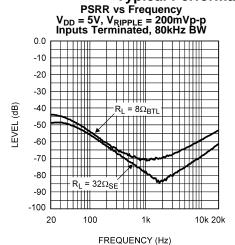

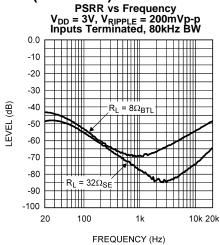

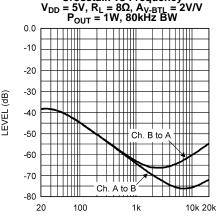

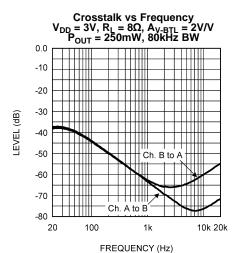

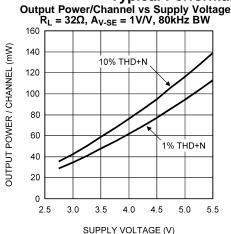

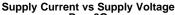

### **Typical Performance Characteristics**

Figure 4.

Figure 5.

THD+N vs Frequency  $V_{DD}$  = 5V,  $R_L$  =  $8\Omega$ ,  $A_{V-BTL}$  = 2V/V  $P_{OUT}$  = 1W/Channel, 80kHz BW

FREQUENCY (Hz) Figure 9.

# TEXAS INSTRUMENTS

Figure 10.

FREQUENCY (Hz) Figure 11.

Figure 12.

Figure 13.

Figure 16.

Figure 17.

Figure 18.

Figure 19.

Figure 21.

# TEXAS INSTRUMENTS

Figure 22.

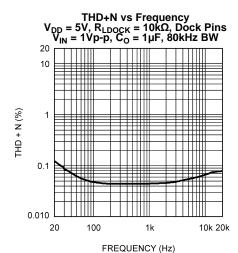

FREQUENCY (Hz) Figure 23.

Figure 24.

Figure 25.

Figure 27.

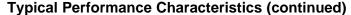

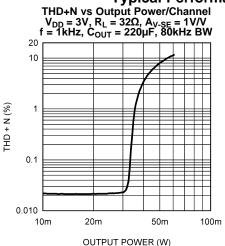

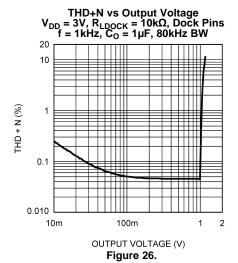

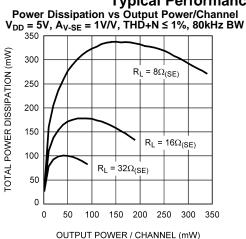

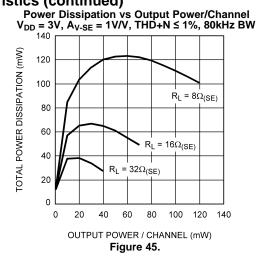

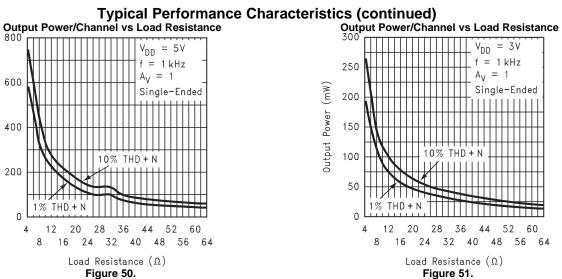

## **Typical Performance Characteristics (continued)**

Figure 28.

Figure 29.

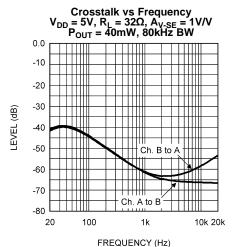

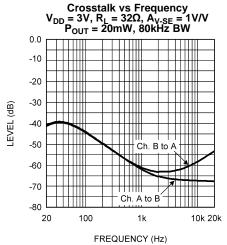

Crosstalk vs Frequency

FREQUENCY (Hz) Figure 30.

Figure 31.

Figure 32.

Figure 33.

# **NSTRUMENTS**

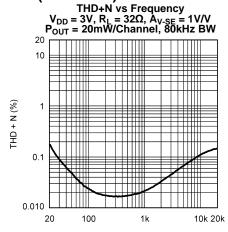

#### Typical Performance Characteristics (continued)

Figure 34.

Figure 35.

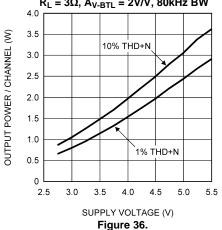

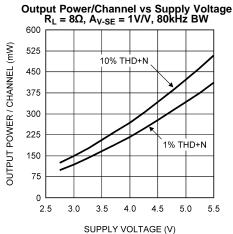

# Output Power/Channel vs Supply Voltage $R_L = 3\Omega$ , $A_{V-BTL} = 2V/V$ , 80kHz BW

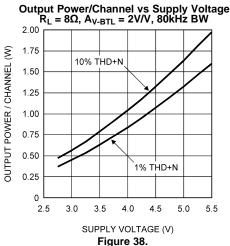

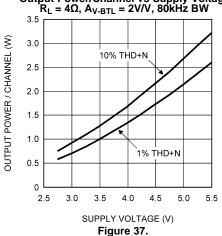

Output Power/Channel vs Supply Voltage  $R_L = 4\Omega$ ,  $A_{V-BTL} = 2V/V$ , 80kHz BW

Figure 39.

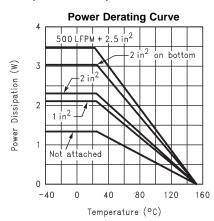

# **Typical Performance Characteristics (continued)**

These curves show the thermal dissipation ability of the LM4936MH at different ambient temperatures given these conditions:

**500LFPM + 2in<sup>2</sup>:** The part is soldered to a 2in<sup>2</sup>, 1 oz. copper plane with 500 linear feet per minute of forced-air flow across it.

**2in<sup>2</sup>on bottom:** The part is soldered to a 2in<sup>2</sup>, 1oz. copper plane that is on the bottom side of the PC board through 21 8 mil vias.

2in<sup>2</sup>: The part is soldered to a 2in<sup>2</sup>, 1oz. copper plane.

1in<sup>2</sup>: The part is soldered to a 1in<sup>2</sup>, 1oz. copper plane.

Not Attached: The part is not soldered down and is not forced-air cooled.

Figure 41.

Figure 40.

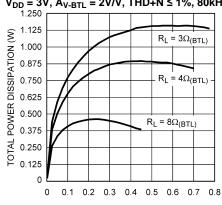

Power Dissipation vs Output Power/Channel V<sub>DD</sub> = 3V, A<sub>V-BTL</sub> = 2V/V, THD+N ≤ 1%, 80kHz BW

OUTPUT POWER / CHANNEL (W) Figure 43.

# TEXAS INSTRUMENTS

### **Typical Performance Characteristics (continued)**

Figure 44.

Figure 46.

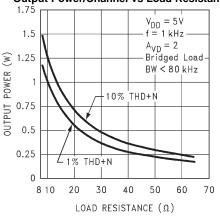

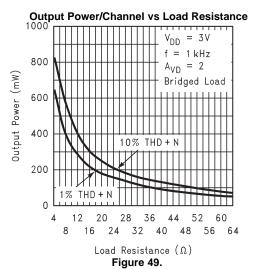

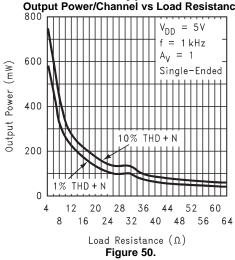

### Output Power/Channel vs Load Resistance

Figure 48.

Submit Documentation Feedback

#### APPLICATION INFORMATION

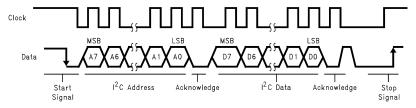

# I<sup>2</sup>C COMPATIBLE INTERFACE

The LM4936 uses a serial bus, which conforms to the I<sup>2</sup>C protocol, to control the chip's functions with two wires: clock (SCL) and data (SDA). The clock line is uni-directional. The data line is bi-directional (open-collector). The maximum clock frequency specified by the I<sup>2</sup>C standard is 400kHz. In this discussion, the master is the controlling microcontroller and the slave is the LM4936.

The I<sup>2</sup>C address for the LM4936 is determined using the ID/CE pin. The LM4936's two possible I<sup>2</sup>C chip addresses are of the form 110110 $X_1$ 0 (binary), where  $X_1 = 0$ , if ID/CE is logic low; and  $X_1 = 1$ , if ID/CE is logic high. If the I<sup>2</sup>C interface is used to address a number of chips in a system, the LM4936's chip address can be changed to avoid any possible address conflicts.

The bus format for the I<sup>2</sup>C interface is shown in Figure 53. The bus format diagram is broken up into six major sections:

The "start" signal is generated by lowering the data signal while the clock signal is high. The start signal will alert all devices attached to the I<sup>2</sup>C bus to check the incoming address against their own address.

The 8-bit chip address is sent next, most significant bit first. The data is latched in on the rising edge of the clock. Each address bit must be stable while the clock level is high.

After the last bit of the address bit is sent, the master releases the data line high (through a pull-up resistor). Then the master sends an acknowledge clock pulse. If the LM4936 has received the address correctly, then it holds the data line low during the clock pulse. If the data line is not held low during the acknowledge clock pulse, then the master should abort the rest of the data transfer to the LM4936.

The 8 bits of data are sent next, most significant bit first. Each data bit should be valid while the clock level is stable high.

After the data byte is sent, the master must check for another acknowledge to see if the LM4936 received the data.

If the master has more data bytes to send to the LM4936, then the master can repeat the previous two steps until all data bytes have been sent.

The "stop" signal ends the transfer. To signal "stop", the data signal goes high while the clock signal is high. The data line should be held high when not in use.

# I<sup>2</sup>C/SPI INTERFACE POWER SUPPLY PIN (I<sup>2</sup>C/SPI V<sub>DD</sub>)

The LM4936's  $I^2C/SPI$  interface is powered up through the  $I^2C/SPI$   $V_{DD}$  pin. The LM4936's  $I^2C/SPI$  interface operates at a voltage level set by the  $I^2C/SPI$   $V_{DD}$  pin which can be set independent to that of the main power supply pin  $V_{DD}$ . This is ideal whenever logic levels for the  $I^2C/SPI$  interface are dictated by a microcontroller or microprocessor that is operating at a lower supply voltage than the main battery of a portable system.

#### HTSSOP PACKAGE PCB MOUNTING CONSIDERATIONS

HTSSOP (die attach paddle) packages provide a low thermal resistance between the die and the PCB to which the part is mounted and soldered. This allows rapid heat transfer from the die to the surrounding PCB copper traces, ground plane and, finally, surrounding air. The result is a low voltage audio power amplifier that produces 2.1W at  $\leq$  1% THD with a 4 $\Omega$  load. This high power is achieved through careful consideration of necessary thermal design. Failing to optimize thermal design may compromise the LM4936's high power performance and activate unwanted, though necessary, thermal shutdown protection.

The packages must have their exposed DAPs soldered to a grounded copper pad on the PCB. The DAP's PCB copper pad is connected to a large grounded plane of continuous unbroken copper. This plane forms a thermal mass heat sink and radiation area. Place the heat sink area on either outside plane in the case of a two-sided PCB, or on an inner layer of a board with more than two layers. Connect the DAP copper pad to the inner layer or backside copper heat sink area with vias. The via diameter should be 0.012in–0.013in with a 1.27mm pitch. Ensure efficient thermal conductivity by plating-through and solder-filling the vias.

Product Folder Links: LM4936

Best thermal performance is achieved with the largest practical copper heat sink area. If the heatsink and amplifier share the same PCB layer, a nominal  $2.5 \text{in}^2$  (min) area is necessary for 5V operation with a  $4\Omega$  load. Heatsink areas not placed on the same PCB layer as the LM4936 should be 5in<sup>2</sup> (min) for the same supply voltage and load resistance. The last two area recommendations apply for 25°C ambient temperature. Increase the area to compensate for ambient temperatures above 25°C. In systems using cooling fans, the LM4936MH can take advantage of forced air cooling. With an air flow rate of 450 linear-feet per minute and a 2.5in<sup>2</sup> exposed copper or 5.0in<sup>2</sup> inner layer copper plane heatsink, the LM4936MH can continuously drive a 3Ω load to full power. In all circumstances and conditions, the junction temperature must be held below 150°C to prevent activating the LM4936's thermal shutdown protection. The LM4936's power de-rating curve in the Typical Performance Characteristics shows the maximum power dissipation versus temperature. Example PCB layouts are shown in the LM4936 MH HTSSOP Board Artwork section. Further detailed and specific information concerning PCB layout, fabrication, and mounting is available in Texas Instruments' AN1187.

#### PCB LAYOUT AND SUPPLY REGULATION CONSIDERATIONS FOR DRIVING 3 $\Omega$ AND 4 $\Omega$ LOADS

Power dissipated by a load is a function of the voltage swing across the load and the load's impedance. As load impedance decreases, load dissipation becomes increasingly dependent on the interconnect (PCB trace and wire) resistance between the amplifier output pins and the load's connections. Residual trace resistance causes a voltage drop, which results in power dissipated in the trace and not in the load as desired. For example,  $0.1\Omega$ trace resistance reduces the output power dissipated by a  $4\Omega$  load from 2.1W to 2.0W. This problem of decreased load dissipation is exacerbated as load impedance decreases. Therefore, to maintain the highest load dissipation and widest output voltage swing, PCB traces that connect the output pins to a load must be as wide as possible.

Poor power supply regulation adversely affects maximum output power. A poorly regulated supply's output voltage decreases with increasing load current. Reduced supply voltage causes decreased headroom, output signal clipping, and reduced output power. Even with tightly regulated supplies, trace resistance creates the same effects as poor supply regulation. Therefore, making the power supply traces as wide as possible helps maintain full output voltage swing.

#### **BRIDGE CONFIGURATION EXPLANATION**

As shown in Figure 3, the LM4936 output stage consists of two pairs of operational amplifiers, forming a twochannel (channel A and channel B) stereo amplifier. (Though the following discusses channel A, it applies equally to channel B.)

Figure 3 shows that the first amplifier's negative (-) output serves as the second amplifier's input. This results in both amplifiers producing signals identical in magnitude, but 180° out of phase. Taking advantage of this phase difference, a load is placed between -OUTA and +OUTA and driven differentially (commonly referred to as "bridge mode"). This results in a differential gain of

$$A_{VD} = 2 * (R_f/R_i)$$

(1)

Bridge mode amplifiers are different from single-ended amplifiers that drive loads connected between a single amplifier's output and ground. For a given supply voltage, bridge mode has a distinct advantage over the singleended configuration: its differential output doubles the voltage swing across the load. This produces four times the output power when compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited or that the output signal is not clipped. To ensure minimum output signal clipping when choosing an amplifier's closed-loop gain, refer to the AUDIO POWER AMPLIFIER DESIGN section.

Another advantage of the differential bridge output is no net DC voltage across the load. This is accomplished by biasing channel A's and channel B's outputs at half-supply. This eliminates the coupling capacitor that single supply, single-ended amplifiers require. Eliminating an output coupling capacitor in a single-ended configuration forces a single-supply amplifier's half-supply bias voltage across the load. This increases internal IC power dissipation and may permanently damage loads such as speakers.

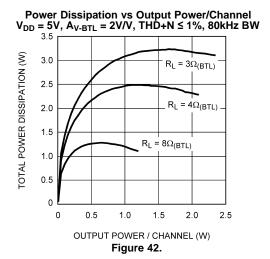

#### POWER DISSIPATION

Copyright © 2005, Texas Instruments Incorporated

Power dissipation is a major concern when designing a successful single-ended or bridged amplifier. Equation 2 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = (V_{DD})^2/(2\pi^2 R_L)$$

Single-Ended

(2)

However, a direct consequence of the increased power delivered to the load by a bridge amplifier is higher internal power dissipation for the same conditions.

The LM4936 has two operational amplifiers per channel. The maximum internal power dissipation per channel operating in the bridge mode is four times that of a single-ended amplifier. From Equation 3, assuming a 5V power supply and a  $4\Omega$  load, the maximum single channel power dissipation is 1.27W or 2.54W for stereo operation.

$$P_{DMAX} = 4 * (V_{DD})^2 / (2\pi^2 R_L) \quad Bridge Mode$$

(3)

The LM4936's power dissipation is twice that given by Equation 2 or Equation 3 when operating in the single-ended mode or bridge mode, respectively due to stereo operation. Twice the maximum power dissipation point given by Equation 3 must not exceed the power dissipation given by Equation 4:

$$P_{DMAX}' = (T_{JMAX} - T_A)/\theta_{JA}$$

(4)

The LM4936's  $T_{JMAX} = 150^{\circ}C$ . In the MH package soldered to a DAP pad that expands to a copper area of  $2\text{in}^2$  on a PCB, the LM4936MH's  $\theta_{JA}$  is 41°C/W. At any given ambient temperature  $T_A$ , use Equation 4 to find the maximum internal power dissipation supported by the IC packaging. Rearranging Equation 4 and substituting  $P_{DMAX}$  for  $P_{DMAX}$  results in Equation 5. This equation gives the maximum ambient temperature that still allows maximum stereo power dissipation without violating the LM4936's maximum junction temperature.

$$T_{A} = T_{JMAX} - 2*P_{DMAX} \theta_{JA}$$

(5)

For a typical application with a 5V power supply and an  $4\Omega$  load, the maximum ambient temperature that allows maximum stereo power dissipation without exceeding the maximum junction temperature is approximately 45°C for the MH package.

$$T_{\text{JMAX}} = P_{\text{DMAX}} \theta_{\text{JA}} + T_{\text{A}} \tag{6}$$

Equation 6 gives the maximum junction temperature  $T_{JMAX}$ . If the result violates the LM4936's 150°C  $T_{JMAX}$ , reduce the maximum junction temperature by reducing the power supply voltage or increasing the load resistance. Further allowance should be made for increased ambient temperatures.

The above examples assume that a device is a surface mount part operating around the maximum power dissipation point.

If the result of Equation 3 multiplied by 2 for stereo operation is greater than that of Equation 4, then decrease the supply voltage, increase the load impedance, or reduce the ambient temperature. If these measures are insufficient, a heat sink can be added to reduce  $\theta_{JA}$ . The heat sink can be created using additional copper area around the package, with connections to the ground pin(s), supply pin and amplifier output pins. External, solder attached SMT heatsinks such as the Thermalloy 7106D can also improve power dissipation. When adding a heat sink, the  $\theta_{JA}$  is the sum of  $\theta_{JC}$ ,  $\theta_{CS}$ , and  $\theta_{SA}$ . ( $\theta_{JC}$  is the junction-to-case thermal impedance,  $\theta_{CS}$  is the case-to-sink thermal impedance, and  $\theta_{SA}$  is the sink-to-ambient thermal impedance.) Refer to the Typical Performance Characteristics curves for power dissipation information at lower output power levels.

#### POWER SUPPLY BYPASSING

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a 5V regulator typically use a 10µF in parallel with a 0.1µF filter capacitor to stabilize the regulator's output, reduce noise on the supply line, and improve the supply's transient response. However, their presence does not eliminate the need for a local 1µF tantalum bypass capacitance connected between the LM4936's supply pins and ground. Do not substitute a ceramic capacitor for the tantalum. Doing so may cause oscillation. Keep the length of leads and traces that connect capacitors between the LM4936's power supply pin and ground as short as possible. Connecting a 1µF capacitor, C<sub>B</sub>, between the BYPASS pin and ground improves the internal bias voltage's stability and the amplifier's PSRR. The PSRR improvements increase as the BYPASS pin capacitor value increases. Too large a capacitor, however, increases turn-on time and can compromise the amplifier's click and pop performance. The selection of bypass capacitor values, especially C<sub>B</sub>, depends on desired PSRR requirements, click and pop performance (as explained in the following section, SELECTING PROPER EXTERNAL COMPONENTS), system cost, and size constraints.

20

#### SELECTING PROPER EXTERNAL COMPONENTS

Optimizing the LM4936's performance requires properly selecting external components. Though the LM4936 operates well when using external components with wide tolerances, best performance is achieved by optimizing component values.

The LM4936 is unity-gain stable, giving a designer maximum design flexibility. The gain should be set to no more than a given application requires. This allows the amplifier to achieve minimum THD+N and maximum signal-to-noise ratio. These parameters are compromised as the closed-loop gain increases. However, low gain circuits demand input signals with greater voltage swings to achieve maximum output power. Fortunately, many signal sources such as audio CODECs have outputs of 1V<sub>RMS</sub> (2.83V<sub>P-P</sub>). Please refer to the AUDIO POWER AMPLIFIER DESIGN section for more information on selecting the proper gain.

#### INPUT CAPACITOR VALUE SELECTION

Amplifying the lowest audio frequencies requires a high value input coupling capacitor (0.33µF in Figure 3), but high value capacitors can be expensive and may compromise space efficiency in portable designs. In many cases, however, the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150 Hz. Applications using speakers with this limited frequency response reap little improvement by using a large input capacitor.

Besides affecting system cost and size, the input coupling capacitor has an effect on the LM4936's click and pop performance. When the supply voltage is first applied, a transient (pop) is created as the charge on the input capacitor changes from zero to a quiescent state. The magnitude of the pop is directly proportional to the input capacitor's size. Higher value capacitors need more time to reach a quiescent DC voltage ( $V_{DD}/2$ ) when charged with a fixed current. The amplifier's output charges the input capacitor through the feedback resistor,  $R_f$ . Thus, pops can be minimized by selecting an input capacitor value that is no higher than necessary to meet the desired –6dB frequency.

As shown in Figure 3, the input resistor ( $R_{IR}$ ,  $R_{IL} = 20k\Omega$ ) and the input capacitor ( $C_{IR}$ ,  $C_{IL} = 0.33\mu F$ ) produce a -6dB high pass filter cutoff frequency that is found using Equation 7.

$$f_{-6 dB} = \frac{1}{2\pi R_{1N} C_1}$$

(7)

As an example when using a speaker with a low frequency limit of 150Hz, the input coupling capacitor, using Equation 7, is  $0.053\mu\text{F}$ . The  $0.33\mu\text{F}$  input coupling capacitor shown in Figure 3 allows the LM4936 to drive a high efficiency, full range speaker whose response extends below 30Hz.

#### OPTIMIZING CLICK AND POP REDUCTION PERFORMANCE

The LM4936 contains circuitry that minimizes turn-on and shutdown transients or "clicks and pops". For this discussion, turn-on refers to either applying the power supply voltage or when the shutdown mode is deactivated. While the power supply is ramping to its final value, the LM4936's internal amplifiers are configured as unity gain buffers. An internal current source changes the voltage of the BYPASS pin in a controlled, linear manner. Ideally, the input and outputs track the voltage applied to the BYPASS pin. The gain of the internal amplifiers remains unity until the voltage on the BYPASS pin reaches  $1/2\ V_{DD}$ . As soon as the voltage on the BYPASS pin is stable, the device becomes fully operational. Although the BYPASS pin current cannot be modified, changing the size of  $C_B$  alters the device's turn-on time and the magnitude of "clicks and pops". Increasing the value of  $C_B$  reduces the magnitude of turn-on pops. However, this presents a tradeoff: as the size of  $C_B$  increases, the turn-on time increases. There is a linear relationship between the size of  $C_B$  and the turn-on time. Below are some typical turn-on times for various values of  $C_B$ :

| Св     | T <sub>ON</sub> |

|--------|-----------------|

| 0.01µF | 2ms             |

| 0.1µF  | 20ms            |

| 0.22μF | 44ms            |

| 0.47µF | 94ms            |

| 1.0µF  | 200ms           |

Product Folder Links: LM4936

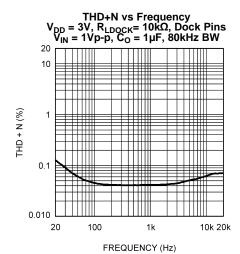

#### **DOCKING STATION INTERFACE**

Applications such as notebook computers can take advantage of a docking station to connect to external devices such as monitors or audio/visual equipment that sends or receives line level signals. The LM4936 has two outputs, Right Dock and Left Dock, which connect to outputs of the internal input amplifiers that drive the volume control inputs. These input amplifiers can drive loads of >1k $\Omega$  (such as powered speakers) with a rail-to-rail signal. Since the output signal present on the RIGHT DOCK and LEFT DOCK pins is biased to  $V_{DD}/2$ , coupling capacitors should be connected in series with the load when using these outputs. Typical values for the output coupling capacitors are 0.33 $\mu$ F to 1.0 $\mu$ F. If polarized coupling capacitors are used, connect their "+" terminals to the respective output pin, see Figure 3.

Since the DOCK outputs precede the internal volume control, the signal amplitude will be equal to the input signal's magnitude and cannot be adjusted. However, the input amplifier's closed-loop gain can be adjusted using external resistors. These  $20k\Omega$  ( $R_{DOCK1}$ ,  $R_{DOCK2}$ ) are shown in Figure 3 and they set each input amplifier's gain to -1. Use Equation 8 to determine the input and feedback resistor values for a desired gain.

$$- A_{VR} = R_{DOCK1}/R_{IN1} \text{ and } - A_{VL} = R_{DOCK2}/R_{IN2}$$

(8)

Adjusting the input amplifier's gain sets the minimum gain for that channel. Although the single ended output of the Bridge Output Amplifiers can be used to drive line level outputs, it is recommended that the R & L Dock Outputs simpler signal path be used for better performance.

#### **BEEP DETECT FUNCTION**

Computers and notebooks produce a system "beep" signal that drives a small speaker. The speaker's auditory output signifies that the system requires user attention or input. To accommodate this system alert signal, the LM4936's beep input pin is a mono input that accepts the beep signal. Internal level detection circuitry at this input monitors the beep signal's magnitude. When a signal level greater than  $V_{DD}/2$  is detected on the BEEP IN pin, the bridge output amplifiers are enabled. The beep signal is amplified and applied to the load connected to the output amplifiers. A valid beep signal will be applied to the load even when MUTE is active. Use the input resistors connected between the BEEP IN pin and the stereo input pins to accommodate different beep signal amplitudes. These resistors ( $R_{\rm BEEP}$ ) are shown as  $200 k\Omega$  values in Figure 3. Use higher value resistors to reduce the gain applied to the beep signal. The resistors must be used to pass the beep signal to the stereo inputs. The BEEP IN pin is used only to detect the beep signal's magnitude: it does not pass the signal to the output amplifiers. The LM4936's shutdown mode must be deactivated before a system alert signal is applied to BEEP IN pin.

### **MICRO-POWER SHUTDOWN**

Shutdown mode is activated when a digital 0 is loaded into the Shutdown bit, B0. When active, the LM4936's micro-power shutdown feature turns off the amplifier's bias circuitry reducing supply current to a typical 0.7µA. Loading a digital 1 into B0 disables shutdown mode. When the LM4936 has power applied, all register bits will have a default value of 0. Because of this, the LM4936 will be in shutdown mode when power is applied.

#### **MODE FUNCTION**

The LM4936's Mode function has two states controlled by bit B2. A digital 0 in bit B2 disables the volume control and forces the LM4936 to function as a fixed gain amplifier. The gain selection is determined by the GAIN SEL bit (B3) While in the fixed gain mode the volume setting has no effect on the output. When a digital 1 is loaded into B2 the output level is determined by the volume control bits. See Table 4 for volume settings.

#### **MUTE FUNCTION**

The LM4936 mutes the amplifier and DOCK outputs when a digital 1 is loaded in bit B1. Even while muted, the LM4936 will amplify a system alert (beep) signal whose magnitude satisfies the BEEP DETECT circuitry. Loading a digital 0 into B1 returns the LM4936 to normal operation.

Product Folder Links: LM4936

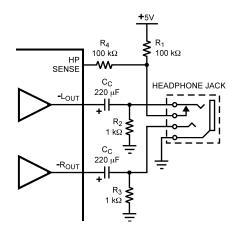

Figure 52. Headphone Sensing Circuit

# HP SENSE FUNCTION ( Headphone In )

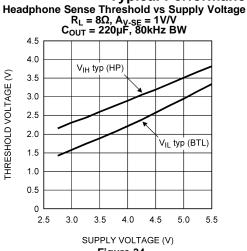

Applying a voltage between the  $V_{IH}$  threshold shown in the graph found in the Typical Performance Characteristics and  $V_{DD}$  to the LM4936's HP SENSE control pin or loading a digital 1 into the HP Control bit (B4) will change the output mode. The '+' outputs will change to be in phase with the '-' outputs instead of 180 degrees out of phase. This action mutes a bridged-connected load since the differential voltage across the load is now close to 0V. The HP SENSE pin over rides the HP Control bit. See Table 2 for more info. Quiescent current consumption is reduced when the IC is in this single-ended mode.

Figure 52 shows the implementation of the LM4936's headphone control function. With no headphones connected to the headphone jack, the R1-R2 voltage divider sets the voltage applied to the HP SENSE pin at approximately 50mV. This 50mV puts the LM4936 into bridged mode operation. The output coupling capacitor blocks the amplifier's half supply DC voltage, protecting the headphones.

The HP SENSE threshold is set so the output signal cannot cause an output mode change. While the LM4936 operates in bridge mode, the DC potential across the load is essentially 0V. Connecting headphones to the headphone jack disconnects the headphone jack contact pin from R2 and allows R1 to pull the HP SENSE pin up to  $V_{DD}$  through R4. This enables the headphone function and mutes the bridged speaker. The single-ended '-' outputs then drive the headphones, whose impedance is in parallel with resistors R2 and R3. These resistors have negligible effect on the LM4936's output drive capability since the typical impedance of headphones is  $32\Omega$ .

Figure 52 also shows the suggested headphone jack electrical connections. The jack is designed to mate with a three-wire plug. The plug's tip and ring should each carry one of the two stereo output signals, whereas the sleeve should carry the ground return. A headphone jack with one control pin contact is sufficient to drive the HP-IN pin when connecting headphones.

#### **GAIN SELECT FUNCTION (Bass Boost)**

The LM4936 features selectable gain, using either internal or external feedback resistors. The GAIN SEL bit (B3) controls which gain is selected. Loading a digital 0 into the GAIN SEL bit sets the gain to internal resulting in a gain of 6dB for BTL mode or unity for singled-ended mode. Loading a digital 1 into the GAIN SEL bit sets the gain to be determined by the external resistors,  $R_{\rm I}$  and  $R_{\rm F}$ .

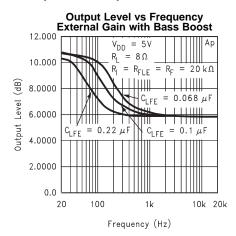

In some cases a designer may want to improve the low frequency response of the bridged amplifier or incorporate a bass boost feature. This bass boost can be useful in systems where speakers are housed in small enclosures. A resistor,  $R_{BS}$ , and a capacitor,  $C_{BS}$ , in parallel, can be placed in series with the feedback resistor of the bridged amplifier as seen in Figure 3.

At low, frequencies  $C_{BS}$  is a virtual open circuit and at high frequencies, its nearly zero ohm impedance shorts  $R_{BS}$ . The result is increased bridge-amplifier gain at low frequencies. The combination of  $R_{BS}$  and  $C_{BS}$  form a -6dB corner frequency at

$$f_{C} = 1/(2\pi R_{BS}C_{BS}) \tag{9}$$

The bridged-amplifier low frequency differential gain is:

$$A_{VD} = 2(R_F + R_{BS}) / R_i$$

(10)

Using the component values shown in Figure 3 ( $R_F = 20k\Omega$ ,  $R_{BS} = 20k\Omega$ , and  $C_{BS} = 0.068\mu F$ ), a first-order, -6dB pole is created at 120Hz. Assuming R  $_i = 20k\Omega$ , the low frequency differential gain is 4V/V or 12dB. The input ( $C_i$ ) and output ( $C_{OUT}$ ) capacitor values must be selected for a low frequency response that covers the range of frequencies affected by the desired bass-boost operation.

#### **VOLUME CONTROL**

The LM4936 has an internal stereo volume control whose setting is a function of the digital values in the V4 – V0 bits. See Table 4.

The LM4936 volume control consists of 31 steps that are individually selected. The range of the steps, are from 0dB - 78dB. The gain levels are 1dB/step from 0dB to -6dB, 2dB/step from -6dB to -36dB, 3dB/step from -36dB to -47dB, 4dB/step from -47dB to -51dB, 5dB/step from -51dB to -66dB, and 12dB to the last step at -78dB.

**Table 4. Volume Control Table**

| Serial Number | V4 | V3 | V2 | V1 | V0 | Gain (dB) |

|---------------|----|----|----|----|----|-----------|

| 0             | 0  | 0  | 0  | 0  | 0  | -90       |

| 1             | 0  | 0  | 0  | 0  | 1  | -90       |

| 2             | 0  | 0  | 0  | 1  | 0  | -68       |

| 3             | 0  | 0  | 0  | 1  | 1  | -63       |

| 4             | 0  | 0  | 1  | 0  | 0  | -57       |

| 5             | 0  | 0  | 1  | 0  | 1  | -51       |

| 6             | 0  | 0  | 1  | 1  | 0  | -47       |

| 7             | 0  | 0  | 1  | 1  | 1  | -45       |

| 8             | 0  | 1  | 0  | 0  | 0  | -42       |

| 9             | 0  | 1  | 0  | 0  | 1  | -39       |

| 10            | 0  | 1  | 0  | 1  | 0  | -36       |

| 11            | 0  | 1  | 0  | 1  | 1  | -34       |

| 12            | 0  | 1  | 1  | 0  | 0  | -32       |

| 13            | 0  | 1  | 1  | 0  | 1  | -30       |

| 14            | 0  | 1  | 1  | 1  | 0  | -28       |

| 15            | 0  | 1  | 1  | 1  | 1  | -26       |

| 16            | 1  | 0  | 0  | 0  | 0  | -24       |

| 17            | 1  | 0  | 0  | 0  | 1  | -22       |

| 18            | 1  | 0  | 0  | 1  | 0  | -20       |

| 19            | 1  | 0  | 0  | 1  | 1  | -18       |

| 20            | 1  | 0  | 1  | 0  | 0  | -16       |

| 21            | 1  | 0  | 1  | 0  | 1  | -14       |

| 22            | 1  | 0  | 1  | 1  | 0  | -12       |

| 23            | 1  | 0  | 1  | 1  | 1  | -10       |

| 24            | 1  | 1  | 0  | 0  | 0  | -8        |

| 25            | 1  | 1  | 0  | 0  | 1  | -6        |

| 26            | 1  | 1  | 0  | 1  | 0  | -5        |

| 27            | 1  | 1  | 0  | 1  | 1  | -4        |

| 28            | 1  | 1  | 1  | 0  | 0  | -3        |

| 29            | 1  | 1  | 1  | 0  | 1  | -2        |

| 30            | 1  | 1  | 1  | 1  | 0  | -1        |

| 31            | 1  | 1  | 1  | 1  | 1  | 0         |

24

#### **AUDIO POWER AMPLIFIER DESIGN**

#### Audio Amplifier Design: Driving 1W into an 8Ω Load

The following are the desired operational parameters:

| Power Output:    | 1 W <sub>RMS</sub>      |

|------------------|-------------------------|

| Load Impedance:  | 8Ω                      |

| Input Level:     | 1 V <sub>RMS</sub>      |

| Input Impedance: | 20 kΩ                   |

| Bandwidth:       | 100 Hz-20 kHz ± 0.25 dB |

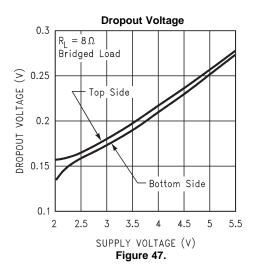

The design begins by specifying the minimum supply voltage necessary to obtain the specified output power. One way to find the minimum supply voltage is to use the Output Power vs Supply Voltage curve in the Typical Performance Characteristics section. Another way, using Equation 10, is to calculate the peak output voltage necessary to achieve the desired output power for a given load impedance. To account for the amplifier's dropout voltage, two additional voltages, based on the Dropout Voltage vs Supply Voltage in the Typical Performance Characteristics curves, must be added to the result obtained by Equation 10. The result is Equation 11.

$$V_{\text{outpeak}} = \sqrt{(2R_L P_0)}$$

(11)

$$V_{DD} \ge (V_{OUTPEAK} + (V_{ODTOP} + V_{ODBOT})) \tag{12}$$

The Output Power vs Supply Voltage graph for an  $8\Omega$  load indicates a minimum supply voltage of 4.6V. This is easily met by the commonly used 5V supply voltage. The additional voltage creates the benefit of headroom, allowing the LM4936 to produce peak output power in excess of 1W without clipping or other audible distortion. The choice of supply voltage must also not create a situation that violates of maximum power dissipation as explained above in the POWER DISSIPATION section.

After satisfying the LM4936's power dissipation requirements, the minimum differential gain needed to achieve 1W dissipation in an  $8\Omega$  load is found using Equation 12.

$$A_{VD} \ge \sqrt{(P_O R_L)}/(V_{IN}) = V_{orms}/V_{inrms}$$

(13)

Thus, a minimum overall gain of 2.83 allows the LM4936's to reach full output swing and maintain low noise and THD+N performance.

The last step in this design example is setting the amplifier's -6dB frequency bandwidth. To achieve the desired  $\pm 0.25dB$  pass band magnitude variation limit, the low frequency response must extend to at least one-fifth the lower bandwidth limit and the high frequency response must extend to at least five times the upper bandwidth limit. The gain variation for both response limits is 0.17dB, well within the  $\pm 0.25dB$  desired limit. The results are

$$f_L = 100Hz/5 = 20Hz$$

(14)

and an

$$f_{H} = 20kHz \times 5 = 100kHz$$

(15)

As mentioned in the SELECTING PROPER EXTERNAL COMPONENTS section, R<sub>i</sub> (Right & Left) and C<sub>i</sub> (Right & Left) create a highpass filter that sets the amplifier's lower bandpass frequency limit. Find the input coupling capacitor's value using Equation 14.

$$C_i \ge 1/(2\pi R_i f_L) \tag{16}$$

The result is

$$1/(2\pi^*20k\Omega^*20Hz) = 0.397\mu F$$

(17)

Use a 0.39µF capacitor, the closest standard value.

Copyright © 2005, Texas Instruments Incorporated

TEXAS INSTRUMENTS

The product of the desired high frequency cutoff (100kHz in this example) and the differential gain  $A_{VD}$ , determines the upper passband response limit. With  $A_{VD}=3$  and  $f_H=100kHz$ , the closed-loop gain bandwidth product (GBWP) is 300kHz. This is less than the LM4936's 3.5MHz GBWP. With this margin, the amplifier can be used in designs that require more differential gain while avoiding performance, restricting bandwidth limitations.

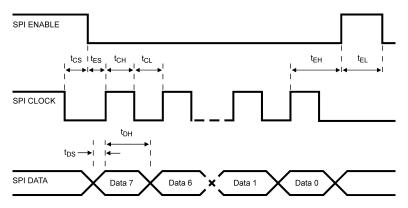

#### **SPI TIMING DIAGRAM**

#### SPI OPERATIONAL REQUIREMENTS

- 1. The maximum clock rate is 5MHz for the CLK pin.

- 2. CLK must remain logic-high for at least 100ns (t<sub>CH</sub>) after the rising edge of CLK, and CLK must remain logic-low for at least 100ns (t<sub>CL</sub>) after the falling edge of CLK.

- 3. Data bits are written to the DATA pin with the most significant bit (MSB) first.

- 4. The serial data bits are sampled at the rising edge of CLK. Any transition on DATA must occur at least 50ns (t<sub>DS</sub>) before the rising edge of CLK. Also, any transition on DATA must occur at least 50ns (t<sub>DH</sub>) after the rising edge of CLK and stabilize before the next rising edge of CLK.

- 5. ENABLE should be logic-low only during serial data transmission.

- 6. ENABLE must be logic-low at least 50ns (t<sub>ES</sub> ) before the first rising edge of CLK, and ENABLE has to remain logic-low at least 50ns (t<sub>EH</sub> ) after the eighth rising edge of CLK.

- 7. If ENABLE remains logic-high for more than 50ns before all 8 bits are transmitted then the data latch will be aborted.

- 8. If ENABLE is logic-low for more than 8 CLK pulses then only the first 8 data bits will be latched and activated at rising edge of eighth CLK.

- 9. ENABLE must remain logic-high for at least 50ns (t<sub>EL</sub>).

- 10. Coincidental rising or falling edges of CLK and ENABLE are not allowed. If CLK is to be held logic-high after the data transmission, the falling edge of CLK must occur at least 50ns (t<sub>CS</sub>) before ENABLE transitions to logic-low for the next set of data.

#### I<sup>2</sup>C TIMING DIAGRAMS

Figure 53. I<sup>2</sup>C Bus Format

26

Figure 54. I<sup>2</sup>C Timing Diagram

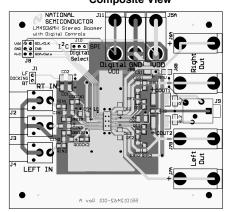

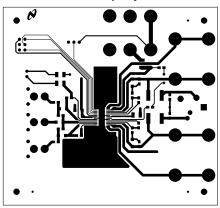

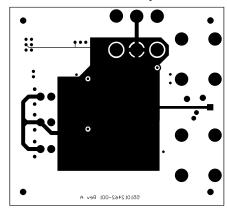

# LM4936 MH HTSSOP Board Artwork(1)(2)

# Composite View

**Top Layer**

Internal Layer 2

#### Silk Screen

INSTRUMENTS

#### Internal Layer 1

**Bottom Layer**

- (1) When driving 3Ω loads from a 5V supply the LM4936MH must be mounted to the circuit board and forced-air cooled. The demo board shown in the datasheet has planes for heat sinking. The top layer plane is 1.05 in² (675mm²), the inner two layers each have a 1.03 in² (667mm²) plane and the bottom layer has a 3.32 in² (2143mm²) plane. The planes are electrically GND and interconnected through six 15 mil vias directly under the package and eight 28 mil vias in various locations.

- (2) When driving 4Ω loads from a 5V supply the LM4936MH must be mounted to the circuit board. The demo board shown in the datasheet has planes for heat sinking. The top layer plane is 1.05 in² (675mm²), the inner two layers each have a 1.03 in² (667mm²) plane and the bottom layer has a 3.32 in² (2143mm²) plane. The planes are electrically GND and interconnected through six 15 mil vias directly under the package and eight 28 mil vias in various locations.

28

## Table 5. LM4936 Board Bill of Materials

| Designator                                             | Value   | Tolerance | Part Description                           | Comment                     |  |  |

|--------------------------------------------------------|---------|-----------|--------------------------------------------|-----------------------------|--|--|

| R <sub>IN1</sub> , R <sub>IN2</sub>                    | 20kΩ    | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| R <sub>I1</sub> , R <sub>I2</sub>                      | 20kΩ    | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| R <sub>F1</sub> , R <sub>F2</sub>                      | 20kΩ    | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| R <sub>DOCK1</sub> , R <sub>DOCK2</sub>                | 20kΩ    | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| R <sub>BS1</sub> , R <sub>BS2</sub>                    | 20kΩ    | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| R <sub>BEEP1</sub> , R <sub>BEEP2</sub>                | 200kΩ   | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| R <sub>L1</sub> , R <sub>L2</sub>                      | 1.5kΩ   | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| R <sub>S</sub> , R <sub>PU</sub>                       | 100kΩ   | 1%        | 1/10W, 0805 Resistor                       |                             |  |  |

| C <sub>IN1</sub> , C <sub>IN2</sub> , C <sub>IN3</sub> | 0.33µF  | 10%       | 10V, Ceramic 1206 Capacitor                |                             |  |  |

| C <sub>BS1</sub> , C <sub>BS2</sub>                    | 0.068µF | 10%       | 10V, Ceramic 1206 Capacitor                |                             |  |  |

| C <sub>S1</sub>                                        | 10μF    | 10%       | 10V, Tantalum 1210 Capacitor               |                             |  |  |

| C <sub>S2</sub> , C <sub>S3</sub> , C <sub>S4</sub>    | 0.1µF   | 10%       | 10V, Tantalum 1206 Capacitor               |                             |  |  |

| C <sub>O1</sub> , C <sub>O2</sub>                      | 1µF     | 10%       | 10V, Electrolytic 1210 Capacitor           |                             |  |  |

| Св                                                     | 1µF     | 10%       | 10V, Tantalum 1210 Capacitor               |                             |  |  |

| C <sub>OUT1</sub> , C <sub>OUT2</sub>                  | 220µF   | 10%       | 16V, Electrolytic 2220 Capacitor           |                             |  |  |

| J <sub>1</sub>                                         |         |           | 0.100 1x2 header, vertical mount           | Docking Outputs             |  |  |

| J <sub>2</sub> , J <sub>3</sub> , J <sub>4</sub>       |         |           | RCA Input Jack, PCB Mount                  | Mouser: 16PJ097             |  |  |

| J <sub>5A</sub>                                        |         |           | Banana-Jack Red, Analog V <sub>DD</sub>    | Mouser: 164-6219            |  |  |

| J <sub>5B</sub>                                        |         |           | Banana-Jack Blck, GND                      | Mouser: 164-6218            |  |  |

| J <sub>6A</sub>                                        |         |           | Banana-Jack Red, Right Out +               | Mouser: 164-6219            |  |  |

| J <sub>6B</sub>                                        |         |           | Banana-Jack Black, Right Out -             | Mouser: 164-6218            |  |  |

| J <sub>7A</sub>                                        |         |           | Banana-Jack Red, Left Out +                | Mouser: 164-6219            |  |  |

| J <sub>7B</sub>                                        |         |           | Banana-Jack Black, Left Out -              | Mouser: 164-6218            |  |  |

| J <sub>8</sub>                                         |         |           | 0.100" 2x3 header, vertical mount          | I <sup>2</sup> C/SPI Inputs |  |  |

| J <sub>9</sub>                                         |         |           | 3.5mm Stereo Headphone Jack                | Shogyo: SJS-0354-5P         |  |  |

| J <sub>10</sub>                                        |         |           | 0.100" 1x3 header, vertical mount          | Digital Select              |  |  |

| J <sub>11</sub>                                        |         |           | Banana Jack — Red, Digital V <sub>DD</sub> | Mouser: 164-6219            |  |  |

## PACKAGE OPTION ADDENDUM

24-.lan-2013

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing |    | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|--------------------|----|-------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing            |    |             | (2)                        |                  | (3)                |              | (4)               |         |

| LM4936MH/NOPB    | ACTIVE | HTSSOP       | PWP                | 28 | 48          | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LM4936MH          | Samples |

| LM4936MHX/NOPB   | ACTIVE | HTSSOP       | PWP                | 28 | 2500        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LM4936MH          | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>&</sup>lt;sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

# PACKAGE MATERIALS INFORMATION

www.ti.com 17-Nov-2012

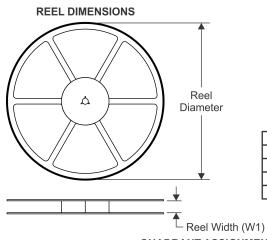

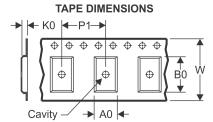

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

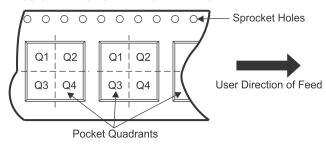

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM4936MHX/NOPB | HTSSOP          | PWP                | 28 | 2500 | 330.0                    | 16.4                     | 6.8        | 10.2       | 1.6        | 8.0        | 16.0      | Q1               |

www.ti.com 17-Nov-2012

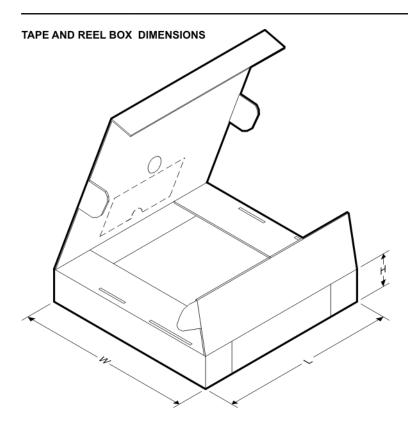

#### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM4936MHX/NOPB | HTSSOP       | PWP             | 28   | 2500 | 349.0       | 337.0      | 45.0        |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.