S54170-B,F,W • N74170-B,F

# DIGITAL 54/74 TTL SERIES

# **DESCRIPTION**

The 54170 and 74170 MSI 16-bit TTL register files incorporate the equivalent of 98 gates on a monolithic chip. The register file is organized as 4 words of 4 bits each and separate on-chip decoding is provided for addressing the four word locations to either write-in or retrieve data. This permits simultaneous writing into one location and reading from another word location.

Four data inputs are available which are used to supply the 4-bit word to be stored. Location of the word is determined by the write address inputs A and B in conjunction with a write-enable signal. Data applied at the inputs should be in its true form. That is, if a high-level signal is desired from the output, a high-level is applied at the data input for that particular bit location. The latch inputs are arranged so that new data will be accepted only if both internal address gate inputs are high. When this condition exists, data at the D input is transferred to the latch output. When the write enable input,  $G_{\rm W}$  is high, the data inputs are inhibited and their states can cause no change in the information stored in the internal latches. When the read enable output,  $G_{\rm R}$ , is high, the data outputs are inhibited and remain high.

The individual address lines permit direct acquisition of data stored in any four of the latches. Four individual decoding gates

are used to complete the address for reading a word. When the read address is made in conjunction with the read-enable signal, the word appears at the four outputs.

This arrangement—data-entry addressing separate from data-read addressing and individual sense line—eliminates recovery times, permits simultaneous reading and writing, and is limited in speed only by the write time (45 nanoseconds maximum) and the read time (35 nanoseconds maximum). The register file has a non-destructive readout in that data is not lost when addressed.

All inputs are buffered to lower the drive requirements to one normalized Series 54/74 load, and input-clamping diodes minimize switching transients to simplify system design. High-speed, double-ended AND-OR-INVERT gates are employed for the read-address function and drive high-sink-current, open-collector outputs. Up to 256 of these outputs may be wire-AND connected for increasing the capacity up to 1024 words. Any number of these registers may be paralleled to provide n-bit word length.

Power dissipation is typically 500 mW total or 5 mW per gate. The 54170 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C; the 74170 is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

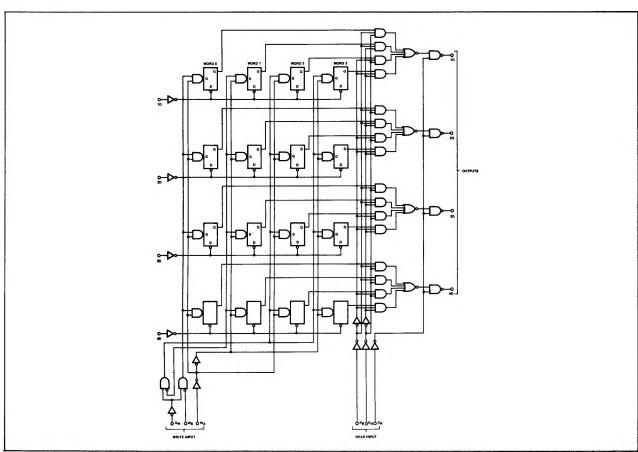

# **LOGIC DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (over operating free-air temperature range unless otherwise noted)

| Supply voltage V <sub>CC</sub> (see N | ote  | 1)   |     |   |  |    |            |     | . 7 V   |

|---------------------------------------|------|------|-----|---|--|----|------------|-----|---------|

| Input voltage (see Note 1)            |      |      |     |   |  |    |            |     | 5.5 V   |

| Output voltage (see Notes             | 1 a  | nd   | 2)  |   |  |    |            |     | 5.5 V   |

| Operating free-air temperar           | ture | e ra | nge | : |  |    |            |     |         |

| 54170 Circuits                        |      |      |     |   |  | -5 | 5°C        | to  | 125° C  |

| 74170 N Circuits .                    |      |      |     |   |  |    | <b>0</b> ° | C t | o 70° C |

| Storage temperature range             |      |      |     |   |  | -6 | 5°C        | to  | 150° C  |

### NOTES:

- 1. Voltage values are with respect to network ground terminal.

- This is the maximum voltage which should be applied to any output when it is in the off state.

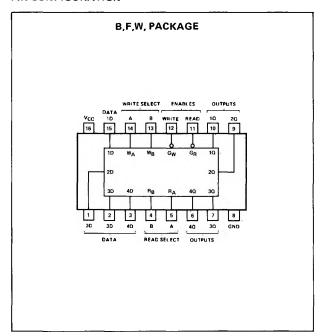

#### **PIN CONFIGURATION**

# RECOMMENDED OPERATING CONDITIONS

|                                                          |                                                                   | 54170 |     |     | 74170 |     |      |          |

|----------------------------------------------------------|-------------------------------------------------------------------|-------|-----|-----|-------|-----|------|----------|

|                                                          |                                                                   | MIN   | МОМ | MAX | MIN   | NOM | MAX  | UNIT     |

| Supply voltage V <sub>CC</sub>                           |                                                                   | 4.5   | 5   | 5.5 | 4.75  | 5   | 5.25 | <b>V</b> |

| Low-level output current, IOL                            |                                                                   |       |     | 16  |       | ,   | 16   | mA       |

| Width of write-enable or read-enable p                   | ulse, t <sub>W</sub>                                              | 25    |     |     | 25    |     |      | ns       |

|                                                          | data input with respect to write enable, t <sub>Setup</sub> (D)   | 10    |     |     | 10    |     |      | ns       |

| Setup times, high- or low-level data (See Note 3)        | write select with respect to write enable, t <sub>Setup</sub> (W) | 15    | :   |     | 15    |     |      | ns       |

|                                                          | read select with respect to read enable, t <sub>setup</sub> (R)   | 5     |     |     | 5     | 1   |      | ns       |

|                                                          | data input with respect to write enable, thold(D)                 | 0     |     |     | 0     |     |      | ns       |

| Hold times, high- or low-level data (See Note 4)         | write select with respect to write enable, thold(W)               | 5     |     |     | 5     |     |      | ns       |

|                                                          | read select with respect to read enable, thold(R)                 | 5     |     |     | 5     |     |      | ns       |

| Latch time for new data, t <sub>latch</sub> (See Note 5) |                                                                   | 25    |     |     | 25    |     |      | ns       |

| Operating free-air temperature range, TA                 |                                                                   | -55   | 25  | 125 | 0     | 25  | 70   | °c       |

#### NOTES:

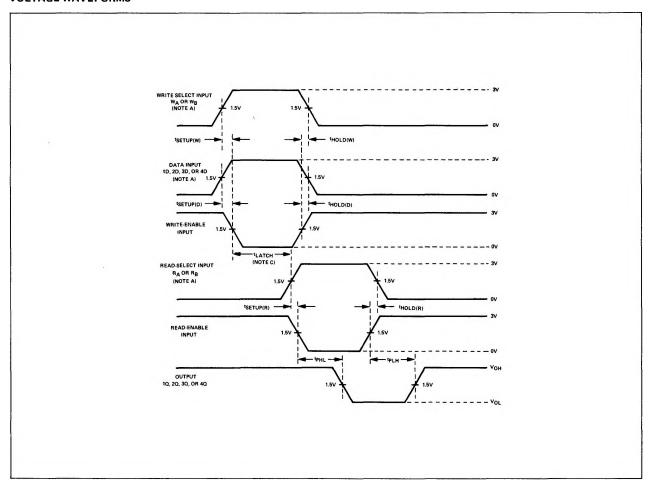

- 3. Setup time is the interval immediately preceding the negative-going edge of the enable pulse during which interval the data or address to be recognized must be maintained at the input to ensure its recognition.

- 4. Hold time is the interval immediately following the positive-going edge of the enable pulse during which interval the data or address to be recognized must be maintained at the input to ensure its continued recognition.

- 5. Latch time is the time required for the internal output of the latch to assume the state of new data. See Figure 1. This is important only when attempting to read from a location immediately after that location has received new data.

# ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                | PARAMETER                              | TEST CONDITIONS†                                   | MIN | TYP‡           | MAX        | UNIT     |

|----------------|----------------------------------------|----------------------------------------------------|-----|----------------|------------|----------|

| VιΗ            | High-level input voltage               |                                                    | 2   |                |            | V        |

| VIL            | Low-level input voltage                |                                                    |     |                | 0.8        | v        |

| Vį             | Input clamp voltage                    | V <sub>CC</sub> = MIN, I <sub>1</sub> = -12 mA     |     |                | -1.5       | v        |

| ЮН             | High-level output current              | $V_{CC} = MIN, V_O = 5.5 V$                        |     |                | 30         | μΑ       |

| VOL            | Low-level output voltage               | $V_{CC}$ = MIN, $V_{IL}$ = 0.8 V, $I_{OL}$ = 16 mA |     |                | 0.4        | V        |

| t <sub>l</sub> | Input current at maximum input voltage | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V      |     |                | 1          | mA       |

| ¹iH            | High-level input current               | $V_{CC} = MAX$ , $V_1 = 2.4 V$                     |     |                | 40         | μΑ       |

| IL             | Low-level input current                | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4 V      |     |                | -1.6       | mA       |

| Icc            | Supply current                         | V <sub>CC</sub> = MAX, 54170<br>see Note 6 74170   |     | 125 ‡<br>125 ‡ | 140<br>150 | mA<br>mA |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable

$\textit{Maximum I}_{\textit{CC}} \textit{ is guaranteed for the following worst-case conditions: 4.5 V} \textit{ is applied to all data inputs and both enable inputs, all } \\$ address inputs are grounded, and all outputs are open.

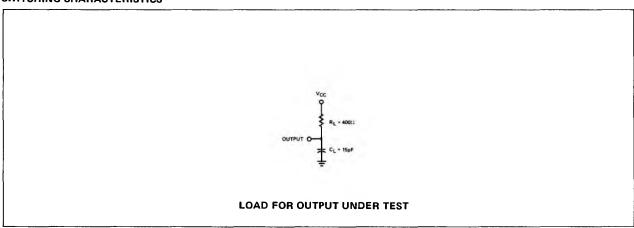

# SWITCHING CHARACTERISTICS, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

| PARAMETER |                                                                                    | TEST (                  | MIN                    | TYP | MAX | UNIT |    |

|-----------|------------------------------------------------------------------------------------|-------------------------|------------------------|-----|-----|------|----|

| tPLH      | Propagation delay time, low-to-<br>high-level output, from read<br>enable to any Q | C <sub>L</sub> = 15 pF, | R <sub>L</sub> = 400 Ω |     | 10  | 15   | ns |

| tPHLq     | Propagation delay time, high-to-low-level output, from read enable to any $\Omega$ | C <sub>L</sub> = 15 pF, | R <sub>L</sub> = 400 Ω |     | 20  | 30   | ns |

# LOGIC

| WRITE FUNCTION TABLE (SEE NOTES A, B, AND C) |        |           |       |              |         |         |  |  |  |  |

|----------------------------------------------|--------|-----------|-------|--------------|---------|---------|--|--|--|--|

| WRI <sup>-</sup>                             | TE INP | UTS<br>GW | 0     | WORD 0 1 2 3 |         |         |  |  |  |  |

| L                                            | L      | L         | O = D | Qn           | Qn      | Qn      |  |  |  |  |

| L                                            | н      | L         | Qn    | Q = D        | $Q_{n}$ | $Q_{n}$ |  |  |  |  |

| н                                            | L      | L         | Ωn    | $Q_{n}$      | Q = D   | $Q_n$   |  |  |  |  |

| н                                            | н      | L         | Ωn    | $Q_{n}$      | $Q_{n}$ | O = D   |  |  |  |  |

| ×                                            | x      | Н         | Qn    | $Q_{n}$      | $Q_{n}$ | $Q_{n}$ |  |  |  |  |

| READ FUNCTION TABLE (SEE NOTES A AND D) |        |                       |                       |      |      |      |  |  |  |

|-----------------------------------------|--------|-----------------------|-----------------------|------|------|------|--|--|--|

| REA<br>RB                               | AD INP | UTS<br>G <sub>R</sub> | OUTPUTS<br>1Q 2Q 3Q 4 |      |      |      |  |  |  |

| L                                       | L      | L                     | W0B1                  | W0B2 | W0B3 | W0B4 |  |  |  |

| L                                       | н      | L                     | W1B1                  | W1B2 | W1B3 | W1B4 |  |  |  |

| н                                       | L      | L                     | W2B1                  | W2B2 | W2B3 | W2B4 |  |  |  |

| Н                                       | н      | L                     | W3B1                  | W3B2 | W3B3 | W3B4 |  |  |  |

| x                                       | х      | Н                     | н                     | н    | Н    | н    |  |  |  |

# NOTES:

- A. H = high level, L = low level, X = irrelevant

- B. (Q = D) = The four selected internal flip flop outputs will assume the states applied to the four external data inputs.

- C. Q<sub>n</sub> = No change.

D. W0B1 = The first bit of word 0, etc.

$<sup>\</sup>ddagger$ Typical power dissipation shown is an average for 50% duty cycle at  $V_{CC}$  = 5 V,  $T_A$  = 25°C.

# **SWITCHING CHARACTERISTICS**

# **VOLTAGE WAVEFORMS**

### NOTES:

- A. Hign-level inputs are illustrated; however, low-level setup and hold times are the same.

- B. Waveforms are supplied by generators with the following characteristics: PRR  $\leq$  1MHz,  $Z_{OUT} \approx 50\Omega$ , duty cycle  $\leq$  50%,  $t_f \leq$  10ns,  $t_f =$  10ns.

- C. This applies only when reading from a location immediately after that location has received new data.