## SINGLE-CHIP MICROCONTROLLER

The  $\mu$ PD17102 is a four-bit single chip microcontroller which has a built-in LCD controller, D/A converter, and operational amplifier. This CPU uses the  $\mu$ PD17000 architecture, allowing data transfer and operation between data memory areas or between data memory areas and peripheral circuits with only one instruction. It also supports 16-bit (1-word) instructions.

#### **FEATURES**

μPD17000 architecture

• Program memory (ROM) : 4K bytes (2048 x 16 bits)

• Data memory (RAM) : 208 words (208 x 4 bits)

Command execution time : 2.0 μs (8 MHz, ceramic/crystal oscillator)

• Interrupting function (Internal: 3, and external: 2)

• 8-bit timer/counter : 2 channels (built-in modulo)

• 8-bit serial interface

2-channel complete CMOS operational amplifier

(Two operation modes available: NORMAL and SAMPLE/HOLD)

- 4-channel multiplexer input comparator --

- 6-bit D/A converter

- Feasible to realize the 4-channel 6-bit A/D conversion function using the above-mentioned comparator and D/A converter

- LCD controller/driver

(14SEGMENT x 2COMMON, 13SEGMENT x 3COMMON, and 12SEGMENT x 4COMMON)

- Zero-cross detection selectable

- Standby function (Stop/Halt)

#### USE:

Electronic rice cooker and blood pressure meter, etc.

#### ORDERING INFORMATION

| Order Code       | Package Package                    |

|------------------|------------------------------------|

| μPD17102G-XXX-00 | 52-pin plastic QFP (bent lead)     |

| μPD17102G-XXX-03 | 52-pin plastic QFP (straight lead) |

#### **OUTLINE OF FUNCTIONS**

μPD17000 architecture

Program memory (ROM): 4K bytes (2048 x 16 bits)

Data memory (RAM) : 222 words (222 x 4 bits)

• Stack level : 3 levels

• Instruction cycle : 2 µs (when operated at 5.0 V and 8 MHz)

e Interrupting function : (Internal: 3, and external: 2)

e 8-bit timer/counter : 2 CH (with modulo integrated)

8-bit serial interface

2-channel complete CMOS operational amplifier

(Two operation modes available: NORMAL and SAMPLE/HOLD)

e 4-channel input comparator with multiplexer

6-bit D/A converter

Feasible to realize 4-channel, 6-bit A/D conversion function using the above-mentioned comparator and D/A converter.

● LCD controller (14SEGMENT x 2COMMON, 13SEGMENT x 3COMMON, and 12SEGMENT x 4COMMON)

Zero-cross detecting function

• Standby function (STOP/HALT)

Data/memory low supply voltage holding function

Oscillator circuit for system clock (ceramic and crystal)

Single power unit (3.0 to 6.0 V, but 4.5 to 6.0 V when the operational amplifier is used)

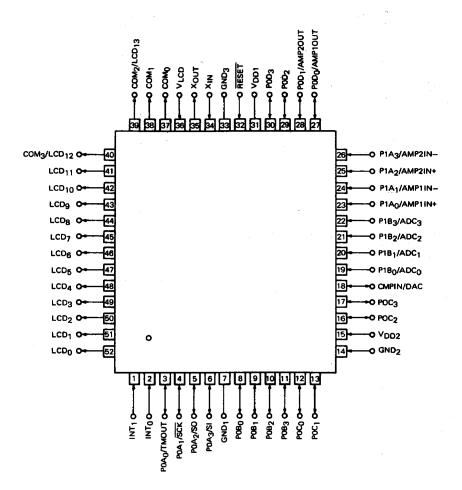

# PIN CONFIGURATION (Top View)

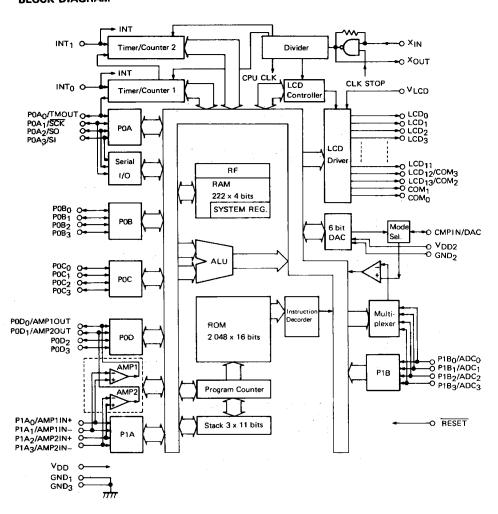

## **BLOCK DIAGRAM**

## 1. OUTLINE

The  $\mu$ PD17102 is a 4-bit single chip microcontroller which integrates all the following circuits on one chip: 4-bit ALU, program memory (ROM), data memory (RAM), I/O ports, timer/event counter, serial interface, vector interrupt circuit.

This chip using the µPD17000 Series architecture has various built-in peripheral circuits including analog circuits, allowing the user to incorporate it into electrical appliances and intelligent units in a distributed system for home automation.

For program development, NEC supports the in-circuit emulator (IE-17K), so that the user can debug programs easily by using the emulator together with the SE board for each product.

#### 2. PIN FUNCTIONS

#### 2.1 Input/Output Ports

## 2.1.1 POA<sub>0</sub> to POA<sub>3</sub> (Port OA): Bi-directional input/output ports

Port 0A is a 4-bit input port (pins from P0A<sub>0</sub> to P0A<sub>3</sub>) with output latch circuits.

This port is mapped to 70H at bank 0 in the data memory space and accessed with normal data memory operation instructions. The direction of input/output is switched for all four bits by the POAGIO value. Setting POAGIO to "1" outputs the value stored at 70H of bank 0 to the pin and setting to "0" disables output and sets input mode. Regardless of the POAGIO value, the pin status can be read with a data memory reference instruction. The contents of the output latch remain unchanged unless the data at 70H of bank 0 is rewritten.

POA<sub>0</sub> is shared by the timer 1 output pin TMOUT. It operates as TMOUT when PTOUTON in the register file is "0" and in normal input/output mode.

When TMOUT is selected, this pin outputs "1" at time 1 reset and reverses the output each time the timer 1 value matches the contents of the modulo register. At this time, this pin is set in output mode regardless of the POAGIO value. The pin status at this time can also be read with a data memory reference instruction. The output latch as POA<sub>0</sub> is independent of TMOUT, and therefore data can be written to 70H of bank 0 even if the pin operates as TMOUT and the data is output when PTOUTON is set to "0" while POAGIO is "1."

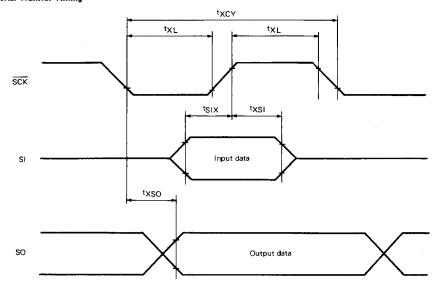

POA<sub>1</sub> to POA<sub>3</sub> are shared by SCK, SO, and SI of the serial interface. The PAO pin is set in normal input/output mode when the SIOON value in the register file is "0" and used as the SIO pin when it is "1."

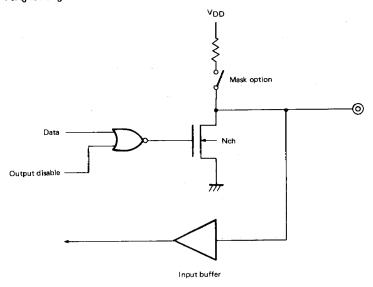

In the port OA input/output format, either of the Nch open/drain input/output or Nch open/drain input/output with a built-in pull-up resistor is selectable by the mask option. In Nch open/drain input/output mode, the port has a 9 V withstanding voltage and is suitable for an interface with a circuit using a different supply voltage. By using the Nch open/drain input/output structure, a 2-wire serial interface can also be used.

When SIOON is "1," data cannot be output to the SCK and SO pins as a port. Even if data is transferred to address 70H of bank 0, this data cannot be input to POA<sub>1</sub> to POA<sub>3</sub>. At this time, only POA<sub>3</sub> is available.

When the  $\overline{SCK}$  pin is in input mode, however, data can be written to the P0A<sub>1</sub> output latch.

Table 2-1 Port 0A functions

| DTOUTON | SIGON | macio  | Write to bank                   | Read from    |                         | Pin fu                  | nction                  |                         |

|---------|-------|--------|---------------------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------|

| PTOUTON | SIOON | POAGIO | 0, 7 <b>0</b> H                 | bank 0, 70H  | POA <sub>0</sub>        | POA <sub>1</sub>        | P0A <sub>2</sub>        | P0A <sub>3</sub>        |

| 0       | 0     | 0      | All four bits are valid.        |              | POA <sub>0</sub><br>IN  | POA <sub>1</sub>        | POA <sub>2</sub>        | POA <sub>3</sub><br>IN  |

|         |       | 1      | All four bits are valid.        |              | P0A <sub>0</sub><br>OUT | POA <sub>1</sub><br>OUT | P0A <sub>2</sub><br>OUT | P0A <sub>3</sub><br>OUT |

|         | 1     | 0      | Only POA <sub>0</sub> is valid. | Enable.      | POA <sub>O</sub>        | SCK                     | so                      | SI                      |

|         |       | 1      | Only POA <sub>0</sub> is valid. |              | P0A <sub>0</sub><br>OUT | SCR SC                  | 30                      |                         |

| 1       | 0     | 0      | All four bits are valid         | (Pin status) |                         | POA <sub>1</sub>        | POA <sub>2</sub><br>IN  | POA <sub>3</sub>        |

|         |       | 1      | All four bits are valid.        |              |                         | P0A <sub>1</sub><br>OUT | POA <sub>2</sub><br>OUT | P0A <sub>3</sub>        |

|         | •     | 0      | Only POA <sub>0</sub> is valid. | 1            | TMOUT                   | SCK                     | so                      | 6.                      |

|         | 1     | 1      | Only POA <sub>0</sub> is valid. |              |                         | SUR                     | 30                      | SI                      |

Note: If data is written to 70H of bank 0 when SIOON is "1," this data can be written to POA<sub>1</sub> only when the SCK pin is in input mode.

## 2.1.2 POB<sub>0</sub> to POB<sub>3</sub> (port OB), POC<sub>0</sub> to POC<sub>3</sub> (port OC): Bi-directional input/output

Ports 0B and 0C are 4-bit input/output pins with output latch circuits: From P0B<sub>0</sub> to P0B<sub>3</sub> and from P0C<sub>0</sub> to P0C<sub>3</sub>. These ports are mapped to 71H and 72H of bank 0 in the data memory space, respectively and are accessed with normal data memory operation instructions like port 0A. The direction of input/output is switched for all 4-bits by the P0BGIO or P0CGIO value in the register file. Setting the value to "1" outputs the data at 71H or 72H of bank 0 to the corresponding pin and "0" disables the output and sets the input mode. Regardless of the P0BGIO and P0CGIO values, the pin status is read when a data memory reference instruction is executed. At this time, the contents of the output latch remain unchanged.

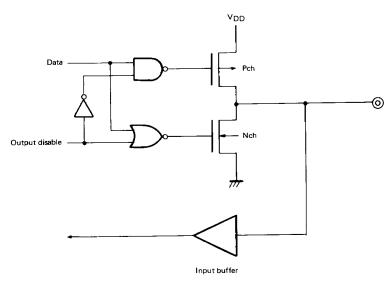

The input/output format of ports OB and OC is the CMOS (push/pull) type.

Table 2-2 Functions of ports 0B and 0C

| POBGIO<br>POCGIO | Input/output<br>direction of pin | Write to bank 0, 71H or 72H | Read from bank 0, 71H or 72H |  |  |

|------------------|----------------------------------|-----------------------------|------------------------------|--|--|

| 0                | Input (output disable)           |                             |                              |  |  |

| 1                | Output                           | Available                   | Available (pin status input) |  |  |

#### 2.1.3 POD<sub>0</sub> to POD<sub>3</sub> (port D): Bi-directional input/output

Port 0D comprises 4-bit input/output pins with output latch circuits. It is mapped to 73H of bank 0 in the data memory space. The input/output direction is switched by the PODGIO value in the register file.

POD<sub>0</sub> is shared with the AMP1 output pin AMP1OUT, and POD<sub>1</sub> is shared with the AMP2 output pin AMP2OUT. These bits are used in normal input/output mode when the AMP1EN or AMP2EN values in the register file are "0" and as AMP1OUT and AMP2OUT respectively when the values are "1."

When AMP10UT and AMP20UT are selected, the pins are used as the AMP10UT and AMP20UT output pins, regardless of the P0DGIO value. A data memory reference instruction reads the pin status regardless of the function selected for the pin. At this time, the pin potential is intermediate, the read value is undefined. The  $\mu$ PD17102 reads only at the moment the instruction is executed and disables other input circuits. Therefore, the through current does not flow through the input circuit.

The POD<sub>0</sub> and POD<sub>1</sub> output latch circuits are independent of AMP1OUT and AMP2OUT. Therefore, data can be written to bank 0, 73H by setting AMP1EN and AMP2EN to "1" even if the pins operate as AMP1OUT and AMP2OUT. When PODGIO is "1," the pins output data as a port by setting AMP1EN and AMP2EN to "0."

The port 0D input/output format is CMOS (push/pull) input/output.

Pin function Read from Write to AP1EN PODGIO bank 0, 73H bank 0, 73H POD<sub>1</sub> POD<sub>2</sub> POD<sub>3</sub> AP2EN POD<sub>o</sub> POD<sub>1</sub> IN POD<sub>2</sub> IN POD<sub>3</sub> IN POD<sub>0</sub> IN 0 0 POD<sub>1</sub> OUT POD<sub>2</sub> OUT POD<sub>3</sub> OUT POD<sub>0</sub> OUT 1 All four bits Enable. POD<sub>3</sub> IN are valid. Pin status. POD<sub>2</sub>IN 0 AMP2OUT AMP1OUT 1 POD<sub>2</sub> OUT POD<sub>3</sub> OUT 1

Table 2-3 Port 0D functions

Note: The AMP output control is selectable for AMP1/2 separately.

#### 2,1,4 P1A<sub>0</sub> to P1A<sub>3</sub> (port 1A): Input

Port 1A comprises 4-bit input pins.

It is mapped to 70H of bank 1 in the data memory space.

P1A<sub>0</sub> and P1A<sub>1</sub> are shared with AMP1 non-reverse input (AMP1IN+) and reverse input (AMP2IN-), P11A and P1A3 are shared with AMP2 non-reverse input (AMP2IN+) and reverse input (AMP2IN-). These pins are not switched and are always connected to both input circuits of the operator amplifier (analog input) and port (digital input).

When used as analog input pins, apply an intermediate potential or AC voltage. If a data memory reference instruction is executed at this time, an undefined value is read. Similar to port 0D, the through current does not flow through the input circuit.

Port 1A has three mask options: With pull-up resistor, with pull-down resistor, and with no built-in resistor. When the pins are used as analog input pins, select the mask option for no built-in resistor. Otherwise, the pins may not operate normally.

Output instructions to the port (data write to 70H in bank 1) are invalid.

Table 2-4 Port 1A function

| Read from bank 1, 70H (logical input) | Write to bank 1, 70H | Analog input                   |

|---------------------------------------|----------------------|--------------------------------|

| Enable                                |                      |                                |

| (Pin status input)                    | Disable              | Always connected to AMP input. |

| (Undefined at intermediate potential) |                      |                                |

#### 2.1.5 P1B<sub>0</sub> to P1B<sub>3</sub> (port 1B): Input

Port 1B comprises 4-bit input pins.

It is mapped to 71H of bank 1 in the data memory space.

Only one of these pins can be set as the input pin of the non-reserve input from the comparator by ADCCH0 and ADCCH1. For more information, see Section 3.12. Similar to ports 0D and 1A, the pin status of port 1B is read with the data memory reference instruction, regardless of the selected pin function, and the through current does not flow through the input circuit even if the intermediate potential is applied.

Port 1B also has three mask options: With pull-up resistor, with pull-down resistor, and with no built-in resistor. When the pins are used as analog input pins, select the mask option for no built-in resistor. Otherwise, the pins may not operate normally.

Output instructions to port 1B (data write to 71H in bank 1) are invalid.

Table 2-5 Port 1B function

| Read from bank 1, 71H (logical input) | Write to bank 1, 71H | Analog input               |

|---------------------------------------|----------------------|----------------------------|

| Enable                                |                      | Either pin is connected to |

| (Pin status input)                    | Disable              | the comparator input       |

| (Undefined at intermediate potential) |                      | (by ADCCH0 and ADCCH1).    |

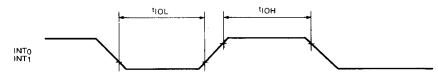

#### 2.2 INT<sub>0</sub>, INT<sub>1</sub>

INT<sub>0</sub> and INT<sub>1</sub> are interrupt request input pins for which the active rising or falling edge is selectable by IEG<sub>0</sub> and IEG<sub>1</sub>. At the rising or falling edge of the INT<sub>0</sub> or INT<sub>1</sub> signal selected by IEG<sub>0</sub> and IEG<sub>1</sub>, the interrupt request flag (IRQ0, IRQ1) is set.

To prevent malfunctions from noise, the pins has a built-in noise remover. The status of the pin for which noise is eliminated by the noise remover is read by referencing  $INT_0$  and  $INT_1$  in the register file with the PEEK instruction, so that the pins are simply used as input pins.

In addition, INT<sub>0</sub>/INT<sub>1</sub> are the count clock input pins of timer 1/2, respectively, and are used when external clocks are selected as timer count clock sources. When sharing the timer input and INT<sub>0</sub>/INT<sub>1</sub> interrupt request input, note that the INT<sub>0</sub>/INT<sub>1</sub> interrupt request flag is also set by the clock.

The INT<sub>1</sub> pin is also used to detect zero-cross when ZCROSS in the register file is set to "1."

## 2.3 CMPIN/DAC, VDD2, GND2

$V_{DD2}$  and  $GND_2$  are pins used to apply the reference voltage of the built-in 6-bit D/A converter. Apply the  $V_{DD}$  potential to  $V_{DD2}$  and the GND potential to  $GND_2$ . These two pins are separated from  $V_{DD}$  and GND and can have separated digital and analog power sources. The applied voltage between the pins is divided into 26 steps (64 steps). The analog value corresponding to digital data stored in four bits of 72H and high-order two bits of 73H of bank 1 in the data memory space is the D/A converter output.

To output the D/A converter data from the CMPIN/DAC pin, set DACEN to "1" and CMPEN to "0" in the register file.

To use a comparator, set DACEN to "0" and CMPEN to "1" in the register file. At this time, the CMPIN/DAC pin operates as the reverse input pin of the comparator (CMPIN). Apply a voltage with the same potential as V<sub>DD</sub> to the V<sub>DD2</sub> pin. Also apply the same potential to GND<sub>2</sub> pin to minimize the current flowing through the D/A converter which is not used.

When using the 6-bit D/A converter under program control, set DACEN to "1" and CMPEN to "1" in the register file. At this time, D/A converter data is not output externally, but is directly input to the comparator reverse input pin. Therefore, the CMPIN/DAC pin is not used.

Table 2-6 V<sub>DD2</sub>, GND<sub>2</sub>, and CMPIN/DAC functions

| DACEN | CMPEN | V <sub>DD2</sub>          | GND <sub>2</sub>          | CMPIN/DAC                 | Function                                             |

|-------|-------|---------------------------|---------------------------|---------------------------|------------------------------------------------------|

| -     |       | V <sub>DD</sub> potential | V <sub>DD</sub> potential | V <sub>DD</sub> potential | D/A converter and comparator are not used.           |

| 0     | 0     | V <sub>DD2</sub>          | GND <sub>2</sub>          | High<br>impedance         | Initial state when the D/A converter is used (Note). |

| 0     | 1     | V <sub>DD</sub> potential | V <sub>DD</sub> potential | CMPIN                     | When the comparator is used.                         |

| 1     | 0     | V <sub>DD2</sub>          | GND <sub>2</sub>          | DAC                       | When the D/A converter is used                       |

| 1     | 1     | V <sub>DD2</sub>          | GND <sub>2</sub>          | V <sub>DD</sub> potential | Used as D/A converter                                |

$<sup>\</sup>mbox{V}_{\mbox{\scriptsize DD}}$  potential indicates that  $\mbox{V}_{\mbox{\scriptsize DD}}$  potential is applied externally.

Note: DACEN and CMPEN are set to "0" at reset.

#### 2.4 V<sub>LCD</sub>

V<sub>LCD</sub> is a power supply pin for driving the liquid crystal display panel (LCD panel).

Depending on the bias method used, it generates the 1/2  $V_{LCD}$ , 1/3  $V_{LCD}$ , and 2/3  $V_{LCD}$  voltages. When using LCD<sub>0</sub> to LCD<sub>13</sub> as the output pins, apply the high voltage under the supply voltage ( $V_{DD}$ ).

# 2.5 LCD<sub>0</sub> to LCD<sub>11</sub>, COM<sub>3</sub>/LCD<sub>12</sub>, COM<sub>2</sub>/LCD<sub>13</sub>, COM<sub>1</sub>, COM<sub>0</sub>

LCD<sub>0</sub> to LCD<sub>11</sub>, COM<sub>3</sub>, LCD<sub>12</sub>, COM<sub>2</sub>/LCD<sub>13</sub>, COM<sub>1</sub>, and COM<sub>0</sub> are LCD panel segment driver pins used to select drive method, such as 14-segment 2-common, 13-segment 3-common, 12-segment 4-common.

LCD<sub>0</sub> to LCD<sub>13</sub> are used as output pins when LCDEN in the register file is "0." At this time, COM<sub>1</sub> and COM<sub>0</sub> are not used.

For more information on the LCD panel, see Section 3.10.

Table 2-7 LCD<sub>0</sub> to LCD<sub>11</sub>, COM<sub>3</sub>/LCD<sub>12</sub>, COM<sub>2</sub>/LCD<sub>13</sub>, COM<sub>1</sub>, and COM<sub>0</sub> functions

| LCDEN | LCD <sub>0</sub> to LCD <sub>11</sub> , COM <sub>3</sub> /LCD <sub>12</sub> , COM <sub>2</sub> /LCD <sub>13</sub> | COM <sub>1</sub> , COM <sub>0</sub> |

|-------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 0     | All are output pins.                                                                                              | Not used                            |

| 1     | LCD drivers and common drivers                                                                                    | Common drivers                      |

#### 2.6 XIN, XOUT

$X_{\text{IN}}$  and  $X_{\text{OUT}}$  are pins used to connect the oscillation vibrator in the system clock generator.

#### 2.7 RESET

RESET is a low-level active reset input pin. The reset has priority over all other operations. In addition to CPU initial start, this pin is also used to release standby mode.

## 2.8 V<sub>DD1</sub>

V<sub>DD1</sub> is a positive power supply pin.

## 2.9 GND<sub>1</sub>, GND<sub>2</sub>

$\mathsf{GND}_1$  and  $\mathsf{GND}_2$  are  $\mathsf{GND}$  potential pins. Wire them so that the same potential is used externally.

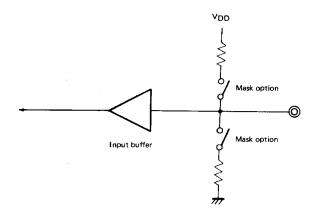

## 2.10 Pin Mask Options

The  $\mu$ PD17102 pins have the mask options listed below. These option can be selected bit according to purpose.

| Pin name                                                                     | Mask option                                                                                                              |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| POA <sub>0</sub> to POA <sub>3</sub>                                         | (1) Nch open-drain input/output (2) Nch open-drain plus built-in pull-up resistor input/output                           |

| P1A <sub>0</sub> to P1A <sub>3</sub><br>P1B <sub>0</sub> to P1B <sub>3</sub> | <ul><li>(1) No built-in resistor</li><li>(2) Built-in pull-up resistor</li><li>(3) Built-in pull-down resistor</li></ul> |

| INT <sub>0</sub>                                                             | <ul><li>(1) No built-in resistor</li><li>(2) Built-in pull-up resistor</li><li>(3) Built-in pull-down resistor</li></ul> |

| RESET                                                                        | (1) No built-in resistor (2) Built-in pull-up resistor                                                                   |

# 2.11 Pin Input/Output Circuits

The Input/output circuit of each pin of the  $\mu PD17102$  is shown below in a partly simplified format:

# (1) POA<sub>0</sub> to POA<sub>3</sub>

# (2) $\ \ \ \mathsf{POB}_0$ to $\mathsf{POB}_3$ , $\mathsf{POC}_0$ to $\mathsf{POC}_3$ , $\mathsf{POD}_0$ to $\mathsf{POD}_3$

(3)  $P1A_0$  to  $P1A_3$ ,  $P1B_0$  to  $P1B_3$ ,  $INT_0$ ,  $INT_1$

(4) RESET

Table 2-8 Digital input/output port pin functions

| PIN NAME                             | 1/0          | COMBINED<br>USE  | FUNCTION                                          | WHEN RESET                     |  |

|--------------------------------------|--------------|------------------|---------------------------------------------------|--------------------------------|--|

| P0A <sub>0</sub>                     |              | TMOUT            |                                                   |                                |  |

| POA <sub>1</sub>                     | 1            | SCK              | 4-bit I/O port (port 0A)                          | High impedance (POAn input     |  |

| POA <sub>2</sub>                     | Input/output | so               | 4-Dit 1/O port (port 0A)                          | Tagy Impossition (For at Impos |  |

| P0A <sub>3</sub>                     | 1            | SI               |                                                   |                                |  |

| POB <sub>O</sub> to POB <sub>3</sub> | Input/output |                  | 4-bit I/O port (port 0B) Large current (15 mA)    | High impedance (input)         |  |

| P0C <sub>0</sub> to P0C <sub>3</sub> | Input/output |                  | 4-bit I/O port (port 0C)<br>Large current (15 mA) | High impedance (input)         |  |

| POD <sub>O</sub>                     |              | AMP1OUT          |                                                   | High impedance (PODn inpu      |  |

| POD <sub>1</sub>                     | Input/output | AMP2OUT          | 4-bit I/O port (port 0D)                          | Trigit impossition (1 050 mp   |  |

| POD <sub>2</sub> to POD <sub>3</sub> | 1            |                  | Middle current (10 mA)                            | High impedance (input)         |  |

| P1A <sub>0</sub>                     |              | AMP1 IN+         |                                                   |                                |  |

| P1A <sub>1</sub>                     | 1            | AMP1IN-          | 4-bit input port (port 1A)                        | Input                          |  |

| P1A <sub>2</sub>                     | Input        | AMP2IN+          | 4-bit input port (port TA)                        | Input                          |  |

| P1A3                                 | 7            | AMP2IN-          |                                                   |                                |  |

| P1B <sub>0</sub>                     |              | ADC <sub>0</sub> |                                                   |                                |  |

| P1B <sub>1</sub>                     | 1            | ADC <sub>1</sub> | 4-bit input port (port 1B)                        | Input                          |  |

| P1B2                                 | Input        | ADC <sub>2</sub> | 4-pit hiput port (port 16)                        | Impor                          |  |

| P1B3                                 |              | ADC <sub>3</sub> |                                                   |                                |  |

Table 2-9 Pins other than port pins

| Pin name                             | Input/output | Shared                               | Function                                                                                                                  | At reset               |  |

|--------------------------------------|--------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| INT <sub>0</sub>                     | Input        |                                      | Used as both the timer 1 count clock input pin and the external interrupt input pin.                                      | Input                  |  |

| INT <sub>1</sub>                     | Input        |                                      | Used as the timer 2 count clock input pin and external interrupt input pin.  Zero-cross detection function is selectable. | Input                  |  |

| TMOUT                                | Output       | POA <sub>O</sub>                     | Timer 1 output pin                                                                                                        | POA <sub>0</sub> input |  |

| SCK                                  | Input/output | POA <sub>1</sub>                     | Serial clock input/output pin                                                                                             | POA <sub>1</sub> input |  |

| SO                                   | Output       | POA <sub>2</sub>                     | Serial data output pin                                                                                                    | POA <sub>2</sub> input |  |

| SI                                   | Input        | POA <sub>3</sub>                     | Serial data input pin                                                                                                     | POA <sub>3</sub> input |  |

| AMP1OUT                              | Output       | POD <sub>0</sub>                     | AMP1 output pin                                                                                                           | POD <sub>0</sub> input |  |

| AMP2OUT                              | Output       | POD <sub>1</sub>                     | AMP2 output pin                                                                                                           | POD <sub>1</sub> input |  |

| AMP1IN+                              |              | P1A <sub>0</sub>                     | AMP1 non-reversed input pin                                                                                               |                        |  |

| AMP1IN-                              |              |                                      | AMP1 reversed input pin                                                                                                   |                        |  |

| AMP2IN+                              | Input        | P1A <sub>2</sub>                     | AMP2 non-reversed input pin                                                                                               | Input                  |  |

| AMP2IN-                              |              | P1A <sub>3</sub>                     | AMP2 reversed input pin                                                                                                   | 1                      |  |

| ADC <sub>0</sub> to ADC <sub>3</sub> | Input        | P1B <sub>0</sub> to P1B <sub>3</sub> | Comparator input pin                                                                                                      | Input                  |  |

| V <sub>DD2</sub>                     | Input        |                                      | D/A converter reference voltage input pin (high-potential side)                                                           |                        |  |

| GND <sub>2</sub>                     | Input        |                                      | D/A converter reference voltage input pin (low-potential side)                                                            |                        |  |

| CMPIN                                | Input/output | DAC                                  | Used as the D/A converter output pin and comparator input pin.                                                            | High impedance         |  |

| LCD <sub>0</sub> to                  | Output       | -                                    | LCD segment driver output pin. Also used as the output port.                                                              | Output                 |  |

| сом3                                 | Output       | LCD <sub>12</sub>                    | Used as the LCD common driver output and LCD segment driver                                                               | Output                 |  |

| COM <sub>2</sub>                     |              | LCD <sub>13</sub>                    | pin. Also used as an output port.                                                                                         | Jupat                  |  |

| COM <sub>0</sub> , COM <sub>1</sub>  | Output       |                                      | LCD common driver output pin                                                                                              | Output                 |  |

| V <sub>LCD</sub>                     | Input        |                                      | LCD driver split potential setting pin                                                                                    | Input                  |  |

| RESET                                | Input        |                                      | System reset input pin                                                                                                    | Input                  |  |

| V <sub>DD1</sub>                     | ,            |                                      | Positive power supply pin                                                                                                 |                        |  |

| GND <sub>1</sub> , GND <sub>3</sub>  |              |                                      | GND potential pin                                                                                                         |                        |  |

| X <sub>IN</sub> , X <sub>OUT</sub>   |              |                                      | System clock oscillator pin                                                                                               | -                      |  |

#### 3. INTERNAL BLOCK

#### 3.1 Program Counter (PC)

The program counter (PC) is an 11-bit binary counter that retains address data of the program memory (ROM).

Fig. 3-1 Program counter configuration

| PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

When the RESET signal goes to low, the PC is set to 0.

Usually, the counter is incremented by one each time an instruction is executed.

The CALL instruction saves the contents of the counter (return address) to the stack memory then loads the branch destination address to the counter. Return instructions (RET, RETSK, and RETI) load the contents of the stack memory (return address) to the counter. The branch instruction (BR) loads the branch destination address to the counter. The ROM data reference instruction (MOVT) temporarily loads the address at which the data to be referenced is stored to the counter. Take care with the level because the contents of the PC are saved to the stack memory immediately before the address is loaded.

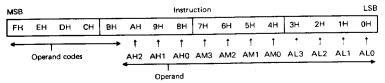

In Fig. 3-2, AHn, AMn, and ALn are addresses indicated by the instruction operand. (See Fig. 3-3.) ARmm is bit n in the address register (ARm) which contains the address to be loaded to the program counter. SP is the stack pointer which points to the contents of the stack memory.

Fig. 3-2 Relationship between instructions and values to be loaded

РСЗ PC2 PC1 PC0 PC6 PC5 PC4 PC10 PC9 PC8 PC7 (SP) (SP) (SP) (SP) (SP) RET, RETSK, RETI (SP) (SP) (SP) (SP) (SP) (SP) ALO AH2 AH1 AH0 АМЗ AM1 AMO AL3 AL2 AL1 BR, CALL AR10 AR03 AR02 AR01 AR00 AR13 AR12 AR11 BR@AR, CALL@AR, MOVT 1 1

Fig. 3-3 Instruction word configuration

#### 7. ASSEMBLER RESERVED WORDS

#### 7.1 Mask Option Pseudo Instructions

For coding  $\mu$ PD17102 programs, a mask option must be specified in Assembler source programs with the mask option pseudo instruction.

The following pins require the mask option:

- P0A<sub>0</sub>, P0A<sub>1</sub>, P0A<sub>2</sub>, P0A<sub>3</sub>

- P1A<sub>0</sub>, P1A<sub>1</sub>, P1A<sub>2</sub>, P1A<sub>3</sub>

- P1B<sub>0</sub>, P1B<sub>1</sub>, P1B<sub>2</sub>, P1B<sub>3</sub>

- INT<sub>0</sub>, INT<sub>1</sub>

- RESET

## 7.1.1 OPTION and ENDOP pseudo instructions

From the OPTION pseudo instruction to the ENDOP pseudo instruction is referred to as the mask option definition block. The format of this block is shown below.

Only the six pseudo instructions explained in Section 7.1.2 can be input to the mask option definition block.

#### Format:

| Symbol field | Mnemonic field | Operand field | Comment field |

|--------------|----------------|---------------|---------------|

| [level:]     | OPTION         |               | [comment:]    |

|              |                |               |               |

|              |                |               |               |

|              | •              |               |               |

|              | •              |               |               |

|              | •              |               |               |

|              | ENDPOP         |               |               |

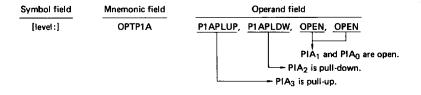

#### 7.1.2 Mask option definition pseudo instructions

Table 7-1 lists the pseudo instruction that are allowed in the mask option definition block. An example for defining the mask option is shown below.

#### Format:

Table 7-1 Mask option definition pseudo instructions

| Pin name                             | Mask option pseudo instruction | Number of parameters | Parameter name                                            |  |  |

|--------------------------------------|--------------------------------|----------------------|-----------------------------------------------------------|--|--|

| POA <sub>0</sub> to POA <sub>3</sub> | OPTP0A                         | 4                    | POAPLUP : Pull up<br>OPEN : Open                          |  |  |

| P1A <sub>0</sub> to P1A <sub>3</sub> | OPTP1A                         | 4                    | P1 APLUP : Pull up<br>P1 APLDW : Pull down<br>OPEN : Open |  |  |

| P1B <sub>0</sub> to P1B <sub>3</sub> | OPTP1B                         | 4                    | P1BPLUP : Pull up<br>P1BPLDW : Pull down<br>OPEN : Open   |  |  |

| ,INT <sub>0</sub>                    | OPTINTO .                      | 1                    | INTOPLUP : Pull up<br>INTOPLDW : Pull down<br>OPEN : Open |  |  |

| INT <sub>1</sub>                     | OPTINT1                        | 1                    | INT1PLUP : Pull up<br>INT1PLDW : Pull down<br>OPEN : Open |  |  |

| RESET                                | OPTRES                         | 1                    | RESPLUP : Pull up OPEN : Open                             |  |  |

#### 7.2 Reserved Symbols

Table 7-2 lists the symbols defined in the  $\mu$ PD17102 device file. These defined symbols include the control register names, port names, and peripheral device names.

- (1) Control registers in register file

- The names of the control register assigned to data memory addresses 80H to BFH in bank 0 are defined. These registers are accessible through the window register (WR) with the PEEK and POKE instructions.

- (2) Registers and ports in data memory Registers assigned to data memory addresses 00H to 7FH, and ports and system registers assigned to 70H and after are defined.

- (3) Peripheral circuits

- Peripheral circuits accessible with the GET and PUT D/A converters are defined.

Table 7-2 List of reserved symbols (1/4)

| NAME  | ATTRIBUTE | VALUE   | R/W | DESCRIPTION                          |  |  |

|-------|-----------|---------|-----|--------------------------------------|--|--|

| DBF3  | MEM       | 0.0CH   | R/W | Bit 15 to bit 12 of data buffer      |  |  |

| DBF2  | MEM       | 0.0DH   | R/W | Bit 11 to bit 8 of data buffer       |  |  |

| DBF1  | MEM       | 0.0EH   | R/W | Bit 7 to bit 4 of data buffer        |  |  |

| DBF0  | MEM       | 0.0FH   | R/W | Bit 3 to bit 0 of data buffer        |  |  |

| AR3   | MEM       | 0.74H   | R   | Bit 15 to bit 12 of address register |  |  |

| AR2   | MEM       | 0.75H   | R   | Bit 11 to bit 8 of address register  |  |  |

| AR1   | MEM       | 0.76H   | R/W | Bit 7 to bit 4 of address register   |  |  |

| AR0   | MEM       | 0.77H   | R/W | Bit 3 to bit 0 of address register   |  |  |

| WR    | MEM       | 0.78H   | R/W | Window register                      |  |  |

| BANK  | MEM       | 0.79H   | R/W | Bank register                        |  |  |

| IXH   | MEM       | 0.7AH   | R/W | Bit 11 to bit 8 of index register    |  |  |

| MPH   | MEM       | 0.7AH   | R/W | Bit 7 to bit 4 of memory pointer     |  |  |

| MPE   | FLG       | 0.7AH.3 | R/W | Memory pointer enable flag           |  |  |

| IXM   | MEM       | 0.7BH   | R/W | Bit 7 to bit 4 of index register     |  |  |

| MPL   | MEM       | 0.7BH   | R/W | Bit 3 to bit 0 of memory pointer     |  |  |

| IXL   | MEM       | 0.7CH   | R/W | Bit 3 to bit 0 of index register     |  |  |

| RPH   | MEM       | 0.7DH   | R/W | Bit 7 to bit 4 of register pointer   |  |  |

| RPL   | MEM       | 0.7EH   | R/W | Bit 3 to bit 0 of register pointer   |  |  |

| PSW   | MEM       | 0.7FH   | R/W | Program status word                  |  |  |

| BCD   | FLG       | 0.7EH.0 | R/W | BCD operation flag                   |  |  |

| CMP   | FLG       | 0.7FH,3 | R/W | Compare flag                         |  |  |

| CY    | FLG       | 0.7FH.2 | R/W | Carry flag                           |  |  |

| Z     | FLG       | 0.7FH.1 | R/W | Zero flag                            |  |  |

| IXE   | FLG       | 0.7FH.0 | R/W | Index register enable flag           |  |  |

| LCDD0 | MEM       | 0.60H   | R/W | LCD segment 0                        |  |  |

| LCDD1 | MEM       | 0.61H   | R/W | LCD segment 1                        |  |  |

| LCDD2 | MEM       | 0.62H   | R/W | LCD segment 2                        |  |  |

| LCDD3 | MEM       | 0.63H   | R/W | LCD segment 3                        |  |  |

| LCDD4 | MEM       | 0.64H   | R/W | LCD segment 4                        |  |  |

| LCDD5 | MEM       | 0.65H   | R/W | LCD segment 5                        |  |  |

| LCDD6 | MEM       | 0.66H   | R/W | LCD segment 6                        |  |  |

Table 7-2 List of reserved symbols (2/4)

| NAME   | ATTRIBUTE | VALUE   | R/W | DESCRIPTION                         |

|--------|-----------|---------|-----|-------------------------------------|

| LCDD7  | MEM       | 0.67H   | R/W | LCD segment 7                       |

| LCDDB  | MEM       | 0.68H   | R/W | LCD segment 8                       |

| LCDD9  | MEM       | 0.69H   | R/W | LCD segment 9                       |

| LCDD10 | MEM       | 0.6AH   | R/W | LCD segment 10                      |

| LCDD11 | MEM       | 0.6BH   | R/W | LCD segment 11                      |

| LCDD12 | MEM       | 0.6CH   | R/W | LCD segment 12                      |

| LCDD13 | MEM       | 0.6DH   | R/W | LCD segment 13                      |

| P0A0   | FLG       | 0.70H.0 | R/W | Port 0A bit 0                       |

| P0A1   | FLG       | 0.70H.1 | R/W | Port 0A bit 1                       |

| P0A2   | FLG       | 0.70H.2 | R/W | Port 0A bit 2                       |

| P0A3   | FLG       | 0.70H.3 | R/W | Port 0A bit 3                       |

| POBO   | FLG       | 0.70H.0 | R/W | Port 0B bit 0                       |

| P0B1   | FLG       | 0.71H.1 | R/W | Port 0B bit 1                       |

| POB2   | FLG       | 0.71H.2 | R/W | Port 0B bit 2                       |

| POB3   | FLG       | 0.71H.3 | R/W | Port 0B bit 3                       |

| POCO   | FLG       | 0.71H.0 | R/W | Port 0C bit 0                       |

| P0C1   | FLG       | 0.72H.1 | R/W | Port 0C bit 1                       |

| P0C2   | FLG       | 0.72H.2 | R/W | Port 0C bit 2                       |

| P0C3   | FLG       | 0.72H.3 | R/W | Port 0C bit 3                       |

| PODO   | FLG       | 0.73H.0 | R/W | Port 0D bit 0                       |

| POD 1  | FLG       | 0.73H.1 | R/W | Port 0D bit 1                       |

| P0D2   | FLG       | 0.73H.2 | R/W | Port 0D bit 2                       |

| P0D3   | FLG       | 0.73H.3 | R/W | Port 0D bit 3                       |

| P1A0   | FLG       | 1.70H.0 | R   | Port 1A bit 0                       |

| P1A1   | FLG       | 1.70H.1 | R   | Port 1A bit 1                       |

| P1A2   | FLG       | 1.70H.2 | R   | Port 1A bit 2                       |

| P1A3   | FLG       | 1.70H.3 | R   | Port 1A bit 3                       |

| P1B0   | FLG       | 1.71H.0 | R   | Port 1B bit 0                       |

| P1B1   | FLG       | 1,71H.1 | R   | Port 1B bit 1                       |

| P1B2   | FLG       | 1.71H.2 | R   | Port 1B bit 2                       |

| P1B3   | FLG       | 1.71H.3 | R   | Port 1B bit 3                       |

| DARH   | MEM       | 1.72H   | R/W | D/A conversion data bit 4 and bit 5 |

Table 7-2 List of reserved symbols (3/4)

| NAME    | ATTRIBUTE | VALUE   | R/W | DESCRIPTION                            |

|---------|-----------|---------|-----|----------------------------------------|

| DARL    | MEM       | 1.73H   | R/W | D/A conversion data bit 3 to bit 0     |

| DACCMP  | FLG       | 1.73H.0 | R   | Result of comparison                   |

| SP      | MEM       | 0.81H   | R/W | Stack pointer                          |

| SIOTS   | FLG       | 0.82H.3 | R/W | SIO operating status                   |

| SIOHIZ  | FLG       | 0.82H.2 | R/W | Status of SO pin                       |

| SIOCK1  | FLG       | 0.82H.1 | R/W | Selection of serial clock              |

| SIOCK0  | FLG       | 0.82H.0 | R/W | Selection of serial clock              |

| INT1    | FLG       | 0.8FH.2 | R   | Status of INT <sub>1</sub> pin         |

| INTO    | FLG       | 0.8FH.1 | R   | Status of INT <sub>0</sub> pin         |

| ZCROSS  | FLG       | 0.8FH.0 | R/W | Status of zero-cross detection circuit |

| TM1EN   | FLG       | 0.91H.3 | R/W | Timer 1 permit                         |

| TM1RES  | FLG       | 0.91H.2 | R/W | Timer 1 reset                          |

| TM1CK1  | FLG       | 0.91H.1 | R/W | Timer 1 clock selection                |

| TM1CK0  | FLG       | 0.91H.0 | R/W | Timer 1 clock selection                |

| TM2EN   | FLG       | 0.92H.3 | R/W | Timer 2 permit                         |

| TM2RES  | FLG       | 0.92H.2 | R/W | Timer 2 reset                          |

| TM2CK1  | FLG       | 0.92H.1 | R/W | Timer 2 clock selection                |

| TM2CK0  | FLG       | 0.92H.0 | R/W | Timer 2 clock selection                |

| IEG1    | FLG       | 0.9FH.2 | R/W | INT1 edge selection                    |

| IEG0    | FLG       | 0.9FH.1 | R/W | INTO edge selection                    |

| AMP1EN  | FLG       | 0.A1H.3 | R/W | AMP1 permit                            |

| AMP1MD2 | FLG       | 0.A1H.2 | R/W | Mode selection                         |

| AMP2MD1 | FLG       | 0.A2H.1 | R/W | Be sure to write "O"                   |

| AMP2MD0 | FLG       | 0.A2H.0 | R/W | SAMPLE-HOLD selection                  |

| CMPEN   | FLG       | 0.A3H.3 | R/W | Comparator permit                      |

| DACEN   | FLG       | 0.A3H.2 | R/W | D/A converter permit                   |

| ADCCH1  | FLG       | 0.A3H.1 | R/W | Comparator input selection             |

| ADCCH0  | FLG       | 0.A3H.0 | R/W | Comparator input selection             |

| PODGIO  | FLG       | 0.A7H,3 | R/W | Port 0D I/O selection                  |

| P0DGIO  | FLG       | 0.A7H.2 | R/W | Port OC I/O selection                  |

| POBGIO  | FLG       | 0.A7H.1 | R/W | Port 0B I/O selection                  |

| P0AGIO  | FLG       | 0.A7H,0 | R/W | Port 0A I/O selection                  |

Table 7-2 List of reserved symbols (4/4)

| NAME    | ATTRIBUTE | VALUE                     | R/W   | DESCRIPTION                 |

|---------|-----------|---------------------------|-------|-----------------------------|

| IPTM2   | FLG       | 0.AEH.1                   | R/W   | INTTM2 permit flag          |

| IP1     | FLG       | 0.AEH.0                   | R/W   | INT1 permit flag            |

| IPSIO   | FLG       | 0.AFH.3                   | R/W   | INTSIO permit flag          |

| IPO .   | FLG       | FLG 0.AFH.2 R/W INTO perr |       | INTO permit flag            |

| IPTM1   | FLG       | 0.AFH.1                   | R/W   | INTTM1 permit flag          |

| LCDOFF  | FLG       | 0.B1H.3                   | R/W   | LCD segment/port selection  |

| LCDMD2  | FLG       | 0.B1H.2                   | R/W   | LCD mode selection          |

| LCDMD1  | FLG       | 0.B1H.1                   | R/W   | LCD mode selection          |

| LCDMD0  | FLG       | 0.B1H.0                   | R/W   | LCD mode selection          |

| LCDEN   | FLG       | 0.B2H.3                   | R/W   | ICD segment output permit   |

| PTOUTON | FLG       | 0.B7H.0                   | : R/W | PTOUT output permit         |

| SIOON   | FLG       | 0.B7H.1                   | R/W   | SIO output permit           |

| IRQTM2  | FLG       | 0.BEH.1                   | R/W   | INTTM2 interrupt request    |

| IRQ1    | FLG       | 0.BEH.0                   | R/W   | INT1 interrupt request      |

| IRQSIO  | FLG       | 0.BFG.3                   | R/W   | INTSIO interrupt request    |

| IRQ0    | FLG.      | 0.BFH.2                   | R/W   | INTO interrupt request      |

| IRQTM1  | FLG       | 0.BFG.1                   | R/W   | INTTM1 interrupt request    |

| DBF     | DAT       | OFH                       | R/W   | GET/PUT instruction operand |

| IX      | DAT       | 01H                       | R/W   | Index register              |

| AR      | DAT       | 00Н                       | R/W   | Address register            |

| SIOSFR  | DAT       | 01H                       | R/W   | SIO register                |

| TM1M    | DAT       | 02H                       | w     | Timer 1 modulo register     |

| TM2M    | DAT       | <b>03</b> H               | w     | Timer 2 modulo register     |

| TMC     | DAT       | 41H                       | R     | Timer count register        |

Note: "W. XYH. Z" in the value field indicates

W ..... Bank

X ..... Row address

Y ..... Colum address

Z ..... Bit

## 8. INSTRUCTION SET

Table 8-1 List of instruction sets

|            | b15 |                                                                                     |                     |      |      |            |

|------------|-----|-------------------------------------------------------------------------------------|---------------------|------|------|------------|

| b14 to b11 | //  |                                                                                     | 0                   |      |      | 1          |

| BIN        | HEX |                                                                                     |                     |      |      |            |

| 0000       | 0   | ADD r,                                                                              | m                   | ADD  | m,   | # i        |

| 0001       | 1   | SUB r,                                                                              | m                   | SUB  | m,   | #i         |

| 0010       | 2   | ADDC r,                                                                             | m                   | ADDC | m,   | #i         |

| 0011       | 3   | SUBC r,                                                                             | m                   | SUBC | m,   | # i        |

| 0100       | 4   | AND r,                                                                              | m                   | AND  | m,   | # i        |

| 0101       | 5   | XOR r,                                                                              | m                   | XOR  | m,   | #i         |

| 0110       | 6   | OR r,                                                                               | m                   | OR   | m,   | # i        |

| 01111      | 7   | INC IX MOVT DI BR @ CALL @ RET RETSK EI DI RETI PUSH AI POP AI GET DI PUT p, PEEK W | BF, @AR<br>AR<br>AR |      |      |            |

| 1000       | 8   | LD r,                                                                               | m                   | ST   | m,   | r          |

| 1001       | 9   | SKE m                                                                               | , #i                | SKGE | m,   | #i         |

| 1010       | Α   | MOV @                                                                               | r, m                | MOV  | m,   | <b>@</b> r |

| 1011       | В   | SKNE m,                                                                             | , #i                | SKLT | m,   | # i        |

| 1100       | С   | BR ad                                                                               | dr                  | CALL | addr |            |

| 1101       | D   |                                                                                     |                     | MOV  | m,   | # i        |

| 1110       | Е   |                                                                                     |                     | SKT  | m,   | #n         |

| 1111       | F   |                                                                                     |                     | SKF  | m,   | #n         |

# Table 8-2 List of INSTRUCTIONS

| Lege                                   | ends                                                                                                                                                    |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R<br>RF<br>AR<br>IX<br>DBF<br>WR<br>MP | : Window register : Memory pointer  MPE : Memory pointer enable flag : Peripheral  Peripheral address ph : Peripheral address high (row address! 3 bits | PC<br>SP<br>STACK<br>BANK<br>(AR) rom<br>INTEF<br>i<br>n<br>addr<br>a <sub>H</sub><br>a <sub>N</sub><br>a <sub>L</sub><br>CY<br>CMP<br>s<br>h | Program counter Stack pointer Stack specified by (SP) Bank register One of program memory data specified by (AR) Interrupt enable flag Immediate data : 4 bits One of program memory address : 11 bits Program memory address high : 3 bits Program memory address high : 3 bits Program memory address high : 4 bits Program memory address low : 4 bits Carry flag Compare flag Stop release condition Halt release condition Address of M.R.RF Contents of M.R.RF, AR, IX, DBF, WR, PE |

|                                        | pt. Peripheral address low (column address) 4 bits                                                                                                      |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| e tion               | 1        |             |                                                         | 0                                                                                                 |                  | Machin          | e code         |                 |

|----------------------|----------|-------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------|-----------------|----------------|-----------------|

| Instruction<br>group | Mnemonic | Operand     | Function                                                | Operation                                                                                         | Opration<br>code | 3bits           | 4bits          | 4bits           |

|                      |          | r,m         | Add memory to register $R$ , $CY \leftarrow (R) + (M)$  |                                                                                                   | 00000            | m <sub>H</sub>  | $m_L$          | r               |

| ı                    | ADD      | m,#i        | Add immediate data to memory                            | M. CY← (M) +i                                                                                     | 10000            | mн              | mL             | i               |

| Addition             |          | r,m         | Add memory to register with carry                       | $R. CY \leftarrow (R) + (M + (CY))$                                                               | 00010            | m <sub>H</sub>  | mL             | r               |

| V∰ V                 | ADDC     | m.#i        | Add immediate data to memory with carry                 | R. CY← (M) +i+ (CY)                                                                               | 10010            | m <sub>H</sub>  | mL             | i               |

|                      |          | AR          | Increment address register                              | AR←AR+1                                                                                           | 00111            | 000             | 1001           | 0000            |

|                      | INC      | IX          | Increment index register                                | IX+1X+1                                                                                           | 00111            | 000             | 1000           | 0000            |

| ٤                    | CUID     | r,m         | Subtract memory from register                           | R. CY+ (R) = (M)                                                                                  | 00001            | m <sub>H</sub>  | mL             | r               |

| Subtraction          | SUB      | m,#i        | Subtract immediate data from memory                     | M. CY← (M) +i                                                                                     | 10001            | m <sub>H</sub>  | mL             | i               |

| 4                    | auna     | r.m         | Subtract memory from register with borrow               | $R. CY \leftarrow (R) - (M) = (CY)$                                                               | 00011            | m <sub>H</sub>  | mL             | r               |

| x.                   | SUBC     | m, #i       | Subtract immediate data from memory with borrow         | M. CY← (M) ~i~ (CY)                                                                               | 10011            | m <sub>H</sub>  | mL             | i               |

| _                    | SKE      | m,#i        | Skip if memory equal to immediate data                  | M-ilskip if zero                                                                                  | 01001            | m <sub>H</sub>  | mL             | i               |

| Comparison           | SKGE     | m,#i        | Skip if memory greater than or equal to immediate data  | M-i,skip if not borrow                                                                            | 11001            | mH              | mL             | i               |

| ашо                  | SKLT     | m,#i        | Skip if memory less than immediate data                 | M-1.skip if borrow                                                                                | 11011            | m <sub>H</sub>  | mL             | i               |

| اتا                  | SKNE     | m,#i        | Skip if memory not equal to immediate data              | M-i.skip if not zero                                                                              | 01011            | m <sub>H</sub>  | m <sub>L</sub> | i,              |

|                      |          | m,#i        | Logical AND of memory and immediate data                | M← (M) AND i                                                                                      | 10100            | m <sub>H</sub>  | mL             | i               |

| operation            | AND      | r,m         | Logical AND of register and memory                      | R← (R) AND (M)                                                                                    | 00100            | m <sup>H</sup>  | mL             | 7               |

| Per s                |          | m.#i        | Logical OR of memory and immediate data                 | M← (M) OR i                                                                                       | 10110            | m <sub>H</sub>  | m <sub>L</sub> | j               |

| ca                   | OR       | r.m         | Logical OR of register and memory                       | R← (R) OR (M)                                                                                     | 00110            | m <sub>H</sub>  | m <sub>L</sub> | Т               |

| Logical              |          | m.#i        | Logical XOR of memory and immediate data                | M← (M) XOR i                                                                                      | 10101            | m <sub>H</sub>  | mL             | i.              |

|                      | XOR      | r,m         | Logical XOR of register and memory                      | R← (R) XOR (M:                                                                                    | 90101            | m <sub>H</sub>  | mL             | r               |

|                      | LD       | r,m         | Load memory to register                                 | R← (M)                                                                                            | 01000            | m <sub>H</sub>  | mı             | r               |

|                      | ST       | m,r         | Store register to memory                                | (M) ←R                                                                                            | 11000            | mH              | mı             | r               |

|                      |          | €r,m        | Move memory to destination memory referring to register | if MPE = 1, $\{(MP), (R)\} \leftarrow (M)$<br>if MPE = 0, $\{(m_H), (R)\} \leftarrow (M)$         | 01010            | mH              | m <sub>L</sub> | r               |

| sfer                 | MOV      | m, er       | Move source memory referring to register to memory      | if MPE = 1, M $\leftarrow$ [ (MP), (R) ]<br>if MPE = 0, M $\leftarrow$ [ (m <sub>H</sub> ), (R) ] | 11010            | mя              | աւ             | r               |

| Transfer             |          | m,#i        | Move immediate data to memory                           | M←i                                                                                               | 11101            | m <sub>H</sub>  | m <sub>L</sub> | i               |

|                      | MOVT     | DBF.<br>éAR | Move ROM data from the address specified in AR to DBF   | sp←(sp) -1.STACK←PC<br>DBF←(AR) rom,<br>PC←STACK,sp←(sp)+1                                        | 00111            | 000             | 0001           | 0000            |

|                      | PUSH     | AR          | Decrement SP, then move AR to stack top                 | SP←(SP) -1,STACK←AR                                                                               | 00111            | 000             | 1101           | 0000            |

|                      | POP      | AR          | Move stack top to AR, then increment SP                 | AR←STACK.SP←SP+1                                                                                  | 00111            | 000             | 1100           | 0000            |

| 1                    | PEEK     | WR.RA       | Get RA from RF through WR                               | WR←(RF)                                                                                           | 00111            | rf <sub>H</sub> | 0011           | rf <sub>L</sub> |

| ction      |          |         |                                                                                      |                                              | 1             | Machin          | e code         | $\Box$         |

|------------|----------|---------|--------------------------------------------------------------------------------------|----------------------------------------------|---------------|-----------------|----------------|----------------|

| Instru     | Mnemonac | Operand | Function                                                                             | Operation                                    | Opration code | 3bits           | 4bits          | 4bits          |

| į          | POKE     | RA,WR   | Put data on WR into RA of RF                                                         | (RF)←WR                                      | 00111         | rf <sub>H</sub> | 0010           | тfL            |

| Transfer   | GET      | DBF.p   | Get peripheral data to DBF                                                           | DBF←p                                        | 00111         | PH              | 1011           | PL             |

| Ĕ          | PUT      | p,DBF   | Put data in DBF to peripheral                                                        | p←DBF                                        | 00111         | PH              | 1010           | PL             |

| Decision   | SKT      | m,#n    | Test memory bits,<br>then skip if all bits specified are true                        | CMP←0<br>skip if M(N) = all "1"              | 11110         | m <sub>H</sub>  | mL             | n              |

|            | SKF      | m, #n   | Test memory bits,<br>then skip if all bits specified are false                       | CMP←0<br>skip if M(N) = all "0"              | 11111         | m <sub>H</sub>  | mL             | л              |

| Branch     | BR       | addr    | Jump to the address                                                                  | PC←ADDR                                      | 01100         | a <sub>H</sub>  | a <sub>M</sub> | a <sub>L</sub> |

| Bra        | DK .     | @AR     | Jump to the address specified in AR                                                  | PC←AR                                        | 00111         | 000             | 0100           | 0000           |

| Shift      | RORC     | r       | Rotate register right with carry $(CY) \rightarrow (R) \rightarrow CY$               |                                              | 00111         | 000             | 0111           | r              |

|            | CALL     | addr    | Call subroutine                                                                      | SP←(SP) -1<br>STACK←((PC)+1),<br>PC←ADDR     | 11100         | a <sub>H</sub>  | a <sub>M</sub> | a <sub>L</sub> |

| Subroutine | CALL     | @AR     | Call subroutine specified in AR                                                      | SP←(SP) - 1,<br>STACK←((PC) + 1),<br>PC←(AR) | 00111         | 000             | 0101           | 0000           |

| Seb        | RET      |         | Return to main routine from subroutine                                               | PC←(STACK),SP←(SP)+1                         | 00111         | 000             | 1110           | 0000           |

|            | RETSK    |         | Return to main routine from subroutine, then skip unconditionary                     | PC←(STACK),SP←(SP)+1<br>and skip             | 00111         | 901             | 1110           | 0000           |

|            | RETI     |         | return to main routine from interrupt service routine PC←(STACK) .SP BANK←(interrupt |                                              | 00111         | 100             | 1110           | 0000           |

| Interrupt  | EI       |         | Enable interrupt                                                                     | INTE flag←1                                  | 00111         | 000             | 1111           | 0000           |

| at a       | DI       |         | Disable interrupt INTE flag ←0                                                       |                                              | 00111         | 001             | 1111           | 0000           |

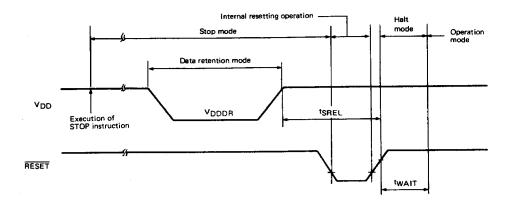

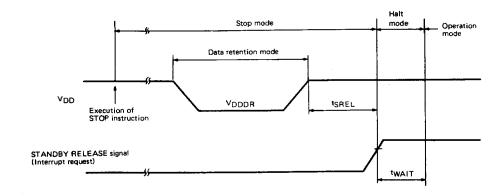

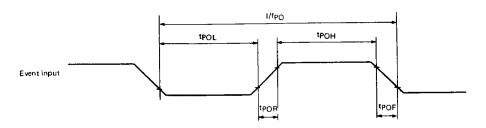

| ا ۾ ا      | STOP     | s       | Stop clock                                                                           | STOP                                         | 00111         | 010             | 1111           | s              |

| Others     | HALT     | h       | Halt the CPU, restart by condition H                                                 | HALT                                         | 00111         | 011             | 1111           | h              |

| Ľ          | NOP      |         | No operation                                                                         | No operation                                 | 00112         | 100             | 1111           | 0000           |

# 9. ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings (Ta = 25 °C)

| Supply Voltage            | $V_{DD}$         | -0.3 to +7.0                  | ٧  | * .                    |          |

|---------------------------|------------------|-------------------------------|----|------------------------|----------|

| Input Voltage             | VI               | -0.3 to V <sub>DD</sub> +0.3  | V  | POA                    | (1)      |

|                           |                  | -0.3 to +11                   | ٧  |                        | (2)      |

|                           |                  | -0.3 to V <sub>DD</sub> + 0.3 | V  | All pins other t       | than POA |

| Output Voltage            | V <sub>O</sub>   | -0.3 to V <sub>DD</sub> +0.3  | ٧  | P0A                    | (1)      |

|                           |                  | -0.3 to +11                   | V  |                        | (2)      |

|                           |                  | -0.3 to V <sub>LCD</sub> +0.3 | ٧  | Segment/comr           | non pins |

|                           |                  | -0.3 to V <sub>DD</sub> +0.3  | ٧  | Pins other than        | above    |

| High-Level Output Current | Іон              | -5                            | mΑ | 1 pin                  |          |

|                           |                  | -20                           | mΑ | Total of all pir       | 15       |

| Low-Level Output Current  | loL              | 15                            | mΑ | 1 pin                  | P0A, P0D |

|                           |                  | 30                            | mΑ |                        | POB, POC |

|                           |                  | 100                           | mΑ | Total of all pir       | ns       |

| Operating Temperature     | Topt             | -40 to +85                    | °C |                        |          |

| Storage Temperature       | T <sub>stq</sub> | -65 to +150                   | °C |                        |          |

| Power Consumption         | Pd               | 190                           | mW | T <sub>a</sub> = 85 °C |          |

|                           |                  |                               |    |                        |          |

Remarks: 1. N-ch open/drain output plus built-in pull-up resistor output

2. N-ch open/drain input/output

# CAPACITY (Ta = 25 °C, VDD = 0 V)

| CHARACTERISTIC        | SYMBOL | MIN. | TYP. | MAX. | UNIT | CONDITION                           |

|-----------------------|--------|------|------|------|------|-------------------------------------|

| Input Capacity        | CIN    |      |      | 15   | pF   | f = 1 MHz                           |

| Output Capacity       | COUT   |      |      | 15   | pF   | Pins other than those measured: 0 V |

| Input/Output Capacity | CIO    |      |      | 15   | pF   |                                     |

# DC CHARACTERISTICS ( $T_a = -40 \text{ to } +85 \,^{\circ}\text{C}$ , $V_{DD} = 3.0 \text{ to } 6.0 \text{ V}$ )

| CHARACTERISTIC                                       | SYMBOL            | MIN.                 | TYP.                  | MAX.                | UNIT | CONDITION                             |                                                            |  |

|------------------------------------------------------|-------------------|----------------------|-----------------------|---------------------|------|---------------------------------------|------------------------------------------------------------|--|

|                                                      | V <sub>IH1</sub>  | 0.8 V <sub>DD</sub>  |                       | 9                   | V    | At SI or SCK                          | input                                                      |  |

| High-Level Input Voltage                             | V <sub>1H2</sub>  | 0.7 V <sub>DD</sub>  |                       | 9                   | ٧    | At POA input                          | 1                                                          |  |

| mign-Lever input voltage                             | V <sub>IH3</sub>  | 0.8 V <sub>DD</sub>  |                       | V <sub>DD</sub>     | ٧    | INT <sub>1</sub> , INT <sub>1</sub> , | RESET                                                      |  |

|                                                      | V <sub>IH4</sub>  | 0.7 V <sub>DD</sub>  |                       | V <sub>DD</sub>     | ٧    | Pins other th                         | an above                                                   |  |

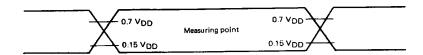

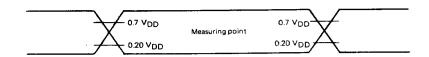

| Law Law Law Malawa                                   | V <sub>IL1</sub>  | 0                    |                       | 0.2 V <sub>DD</sub> | V    | SI, SCK, INT                          | O, INT <sub>1</sub> , RESET                                |  |

| Low-Level Input Voltage                              | V <sub>IL2</sub>  | 0                    |                       | 0.3 V <sub>DD</sub> | V    | Pins other the                        | an above                                                   |  |

| High-Level Output Voltage                            | Voн               | V <sub>DD</sub> -2.0 | V <sub>DD</sub> −0.4  |                     | ٧    |                                       | V <sub>DD</sub> = 4.5 to 6.0 V<br>I <sub>OH</sub> = -1 mA  |  |

|                                                      |                   | V <sub>DD</sub> 1.0  | V <sub>DD</sub> -0.04 |                     | ٧    |                                       | I <sub>OH</sub> = -100 μA                                  |  |

|                                                      |                   |                      | 0.85                  | 2.0                 | ٧    | POB, POC                              | V <sub>DD</sub> = 4.5 to 6.0 V<br>I <sub>OL</sub> = 15 mA  |  |

|                                                      |                   |                      | 0.06                  | 0.5                 | ٧    |                                       | I <sub>OL</sub> = 600 μA                                   |  |

| Low-Level Output Voltage                             | VOL               |                      | 0.85                  | 2.0                 | >    |                                       | V <sub>DD</sub> = 4.5 to 6.0 V<br>I <sub>OL</sub> = 10 mA  |  |

|                                                      |                   |                      | 0.15                  | 0.4                 | V    | POA, POD                              | V <sub>DD</sub> = 4.5 to 6.0 V<br>I <sub>OL</sub> = 1.6 mA |  |

|                                                      |                   |                      | 0.04                  | 0.5                 | v    |                                       | I <sub>OL</sub> = 400 μA                                   |  |

| Ulah Lauri                                           | <sup>1</sup> LIH1 |                      |                       | 3                   | μА   | Other than<br>XI and XO               | V <sub>IN</sub> = V <sub>DD</sub>                          |  |

| High-Level Input Leak Current                        | LIH2              |                      |                       | 10                  | μА   | XI, XO                                | V <sub>IN</sub> = V <sub>DD</sub>                          |  |

|                                                      | ILIH3             |                      |                       | 10                  | μΑ   | POA (3)                               | V <sub>IN</sub> = 9 V                                      |  |

| Low-Level Input Leak Current                         | LIL               |                      |                       | -3                  | μΑ   | Other than<br>XI and XO               | V <sub>IN</sub> = 0 V                                      |  |