NEC

### PRELIMINARY DATA SHEET

### **MOS INTEGRATED CIRCUIT**

## µPD65977S1-xxx-B6

### SYSTEM-ON-CHIP LITE GATE ARRAY WITH ARM7TDMI SUBSYSTEM HARDWARE

### DESCRIPTION

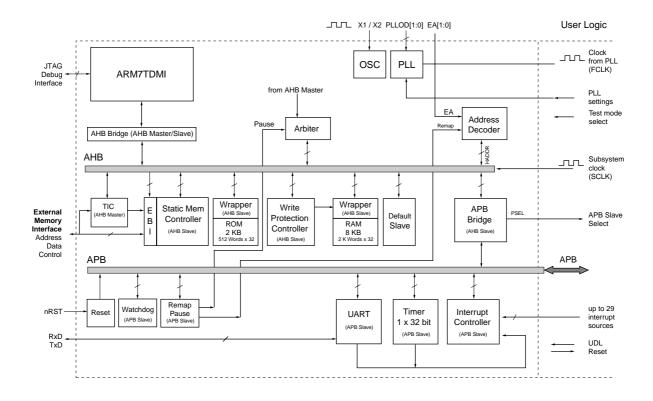

The System-on-Chip Lite ("SoCLite") is based on standard ASIC technology and consists of two blocks: an ARM7TDMI based subsystem and a sea-of-gates area. The ARM subsystem is fully designed and verified as a supermacro. It frees the user from the task of developing a complete RISC computer system. The sea-of-gates area allows the user to implement custom logic or special peripheral functions.

The SoCLite is designed for embedded control applications. To maintain flexibility, SoCLite is not realized as an ASSP (Application Specific Standard Product), this means that it can be used for a wide range of different applications. Once the customer functions are implemented into the sea-of-gates, it becomes a custom SoC.

The ARM7TDMI based subsystem of SoCLite offers a basic combination of general purpose peripheral functions, like a serial communication interface (UART), Timer (32-bit), Interrupt Controller, Watchdog, internal RAM and ROM (only as boot-ROM).

Functions in detail are described in the following user's manual. Be sure to read this manual when you design your systems.

System-on-Chip Lite User's Manual - Hardware : A15402EE1V0UM00

### FEATURES

- 32-bit RISC CPU with Von Neumann Architecture

- Internal 2 Kbyte ROM (boot ROM only)

- Internal 8 Kbyte RAM

- Serial Interface

- UART mode: 1 channel

- Timer

- 32-bit timer with load register: 1 channel

Watchdog timer: 1 channel

- Interrupt Controller with 32 prioritized interrupt sources

- External Bus Interface (32-bit data / 26-bit address

- bus)On-chip debug capability via JTAG

- Built-in power saving mode

- Power supply voltage range: 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V

- Frequency range: up to 35 MHz for ARM subsystem

- Crystal frequency range: 4 MHz ≤ f<sub>CRYSTAL</sub> ≤ 16 MHz

- Built-in clock oscillator circuit with internal PLL

PLL output: 6.25 MHz to 115 MHz

- Temperature range: -40 °C to +85 °C

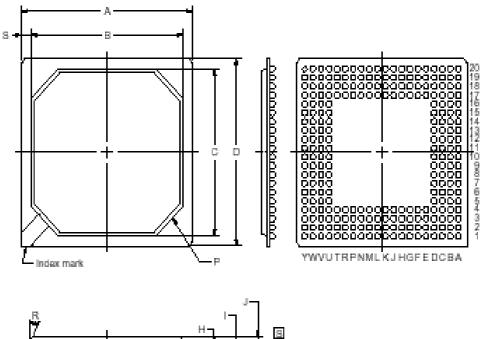

- Package: 256 Plastic BGA, (27 x 27 mm)

- Process: CMOS-9HD

- Sea-of-Gates: 190K raw gates for user defined logic

### **ORDERING INFORMATION**

| Device  | Part Number       | Package                | ROM          | RAM | Oper. Freq. |

|---------|-------------------|------------------------|--------------|-----|-------------|

| SoCLite | µPD65977S1-xxx-B6 | 256 PBGA<br>27 x 27 mm | 2 K boot ROM | 8 K | 35 MHz      |

The information contained in this document is released in advance of the production cycle for the device. The parameters for the device may change before final production, or NEC Corporation may, at its own discretion, withdraw the device prior to production.

### INTERNAL BLOCK DIAGRAM

### **PIN IDENTIFICATION**

| XADDR0 to XADDR25 | : Memory Address Bus                                 | AV <sub>DD</sub>                      | : Analog Power Supply for PLL  |

|-------------------|------------------------------------------------------|---------------------------------------|--------------------------------|

| XDATA0 to XDATA31 | : Memory Data Bus                                    | $DV_DD$                               | : Digital Power Supply for PLL |

| nXCS0 to nXCS7    | : Memory Chip (Bank) Select                          | AV <sub>SS</sub>                      | : Analog Ground for PLL        |

| nXBLS0 to nXBLS3  | : Memory Byte Lane Select                            | $DV_SS$                               | : Digital Ground for PLL       |

| nXOE              | : Memory Output Enable                               | $V_{\text{DD0}}$ to $V_{\text{DD11}}$ | : Power Supply                 |

| nXWEN             | : Memory Read / Write                                | $\rm V_{SS0}$ to $\rm V_{SS12}$       | : Ground Power Supply          |

| nXWAIT            | : Memory Wait                                        | IC1                                   | : Internal connection          |

| RXD               | : Receive Data Input                                 | TEST                                  | : Internal connection          |

| TXD               | : Transmit Data Output                               |                                       |                                |

| X1                | : Crystal                                            |                                       |                                |

| X2                | : Crystal                                            |                                       |                                |

| nRST              | : Reset                                              |                                       |                                |

| EA0               | Enable signal for external or internal boot memory   |                                       |                                |

| EA1               | . Enable signal for external or internal boot memory |                                       |                                |

| DBGEN             | : Debug enable                                       |                                       |                                |

| PLLOD0            | . Frequency range of PLL output                      |                                       |                                |

| PLLOD1            | . Frequency range of PLL output                      |                                       |                                |

| JTAG_TDI          | : JTAG data in                                       |                                       |                                |

| JTAG_TDO          | : JTAG data out                                      |                                       |                                |

| JTAG_TCK          | : JTAG clock                                         |                                       |                                |

| JTAG_TMS          | : JTAG mode select                                   |                                       |                                |

| JTAG_TRST         | : JTAG reset                                         |                                       |                                |

| TCLK              | : Clock for test purposes                            |                                       |                                |

|                   |                                                      |                                       |                                |

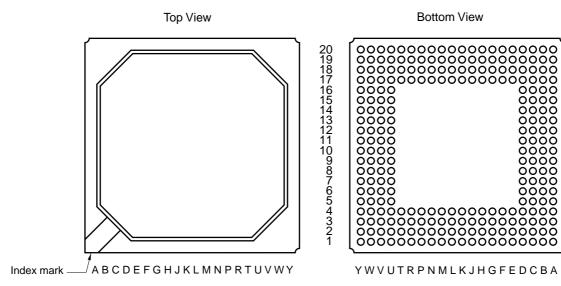

### **PIN CONFIGURATION**

• 256-Pin Plastic BGA (27 mm × 27 mm)

| (1    | /3)   |

|-------|-------|

| · · · | · - / |

| Pin<br>Number | Pin Name             | Pin<br>Number | Pin Name             | Pin<br>Number | Pin Name             | Pin<br>Number | Pin Name         |

|---------------|----------------------|---------------|----------------------|---------------|----------------------|---------------|------------------|

| A1            | V <sub>SS0</sub>     | D5            | nXCS5                | L1            |                      | U17           | V <sub>SS7</sub> |

| A2            | XDATA31              | D6            | V <sub>DD11</sub>    | L2            |                      | U18           |                  |

| A3            | XDATA29              | D7            | nXCS0                | L3            |                      | U19           |                  |

| A4            | XDATA27              | D8            | V <sub>SS12</sub>    | L4            |                      | U20           |                  |

| A5            | nXCS2                | D9            | XADDR22              | L17           | V <sub>DD7</sub>     | V1            |                  |

| A6            | XDATA25              | D10           | XADDR20              | L18           | IC1 <sup>Note1</sup> | V2            |                  |

| A7            | XDATA24              | D11           | V <sub>DD10</sub>    | L19           | nXBLS1               | V3            |                  |

| A8            | XDATA22              | D12           | XADDR16              | L20           | nXBLS0               | V4            |                  |

| A9            | XDATA20              | D13           | V <sub>SS11</sub>    | M1            |                      | V5            |                  |

| A10           | XDATA18              | D14           | PLLOD0               | M2            |                      | V6            |                  |

| A11           | XDATA17              | D15           | V <sub>DD9</sub>     | M3            |                      | V7            |                  |

| A12           | XDATA15              | D16           | IC1 <sup>Note1</sup> | M4            |                      | V8            |                  |

| A13           | XDATA14              | D17           | V <sub>SS10</sub>    | M17           | JTAG_TDO             | V9            |                  |

| A14           | XDATA13              | D18           | XADDR10              | M18           | JTAG_TDI             | V10           |                  |

| A15           | XDATA12              | D19           | XADDR9               | M19           | TXD                  | V11           |                  |

| A16           | IC1 <sup>Note1</sup> | D20           | XDATA8               | M20           | RXD                  | V12           |                  |

### SoCLite

(2/3)

| Pin<br>Number | Pin Name              | Pin<br>Number | Pin Name         | Pin<br>Number | Pin Name         | Pin<br>Number | Pin Name |

|---------------|-----------------------|---------------|------------------|---------------|------------------|---------------|----------|

| A17           | AV <sub>SS</sub>      | E1            |                  | N1            |                  | V13           |          |

| A18           | DV <sub>DD</sub>      | E2            |                  | N2            |                  | V14           |          |

| A19           | X1                    | E3            |                  | N3            |                  | V15           |          |

| A20           | nRST                  | E4            |                  | N4            | V <sub>SS3</sub> | V16           |          |

| B1            |                       | E17           | XADDR8           | N17           | V <sub>SS8</sub> | V17           |          |

| B2            | TCLK                  | E18           | XADDR7           | N18           | JTAG_TRST        | V18           |          |

| B3            | XDATA30               | E19           | XDATA7           | N19           | JTAG_TMS         | V19           |          |

| B4            | XDATA28               | E20           | XDATA6           | N20           | JTAG_TCK         | V20           |          |

| B5            | nXCS3                 | F1            |                  | P1            |                  | W1            |          |

| B6            | XDATA26               | F2            |                  | P2            |                  | W2            |          |

| B7            | XADDR24               | F3            |                  | P3            |                  | W3            |          |

| B8            | XDATA23               | F4            | V <sub>DD0</sub> | P4            |                  | W4            |          |

| B9            | XDATA21               | F17           | V <sub>DD8</sub> | P17           |                  | W5            |          |

| B10           | XDATA19               | F18           | XADDR6           | P18           |                  | W6            |          |

| B11           | XADDR17               | F19           | XADDR5           | P19           |                  | W7            |          |

| B12           | XDATA16               | F20           | XDATA5           | P20           |                  | W8            |          |

| B13           | XADDR13               | G1            |                  | R1            |                  | W9            |          |

| B14           | XADDR11               | G2            |                  | R2            |                  | W10           |          |

| B15           | PLLOD1                | G3            |                  | R3            |                  | W11           |          |

| B16           | $DV_{SS}$             | G4            |                  | R4            | V <sub>DD2</sub> | W12           |          |

| B17           | EA1                   | G17           | XADDR4           | R17           | V <sub>DD6</sub> | W13           |          |

| B18           | X2                    | G18           | XADDR3           | R18           |                  | W14           |          |

| B19           | TEST <sup>Note2</sup> | G19           | XDATA4           | R19           |                  | W15           |          |

| B20           | XDATA11               | G20           | XDATA3           | R20           |                  | W16           |          |

| C1            |                       | H1            |                  | T1            |                  | W17           |          |

| C2            |                       | H2            |                  | T2            |                  | W18           |          |

| C3            | nXCS7                 | H3            |                  | Т3            |                  | W19           |          |

| C4            | nXCS6                 | H4            | V <sub>SS2</sub> | T4            |                  | W20           |          |

| C5            | nXCS4                 | H17           | V <sub>SS9</sub> | T17           |                  | Y1            |          |

| C6            | nXCS1                 | H18           | XADDR2           | T18           |                  | Y2            |          |

| C7            | XADDR25               | H19           | XDATA2           | T19           |                  | Y3            |          |

| C8            | XADDR23               | H20           | XDATA1           | T20           |                  | Y4            |          |

| C9            | XADDR21               | J1            |                  | U1            |                  | Y5            |          |

# NEC

(3/3)

| Pin<br>Number | Pin Name             | Pin<br>Number | Pin Name         | Pin<br>Number | Pin Name         | Pin<br>Number | Pin Name |

|---------------|----------------------|---------------|------------------|---------------|------------------|---------------|----------|

| C10           | XADDR19              | J2            |                  | U2            |                  | Y6            |          |

| C11           | XADDR18              | J3            |                  | U3            |                  | Y7            |          |

| C12           | XADDR15              | J4            |                  | U4            | V <sub>SS4</sub> | Y8            |          |

| C13           | XADDR14              | J17           | XADDR1           | U5            |                  | Y9            |          |

| C14           | XADDR12              | J18           | XADDR0           | U6            | V <sub>DD3</sub> | Y10           |          |

| C15           | IC1 <sup>Note1</sup> | J19           | XDATA0           | U7            |                  | Y11           |          |

| C16           | AV <sub>DD</sub>     | J20           | nXWAIT           | U8            | V <sub>SS5</sub> | Y12           |          |

| C17           | EA0                  | K1            |                  | U9            |                  | Y13           |          |

| C18           | DBGEN                | K2            |                  | U10           | V <sub>DD4</sub> | Y14           |          |

| C19           | XDATA10              | КЗ            |                  | U11           |                  | Y15           |          |

| C20           | XDATA9               | K4            | V <sub>DD1</sub> | U12           |                  | Y16           |          |

| D1            |                      | K17           | nXOE             | U13           | V <sub>SS6</sub> | Y17           |          |

| D2            |                      | K18           | nXWEN            | U14           |                  | Y18           |          |

| D3            |                      | K19           | nXBLS3           | U15           | V <sub>DD5</sub> | Y19           |          |

| D4            | V <sub>SS1</sub>     | K20           | nXBLS2           | U16           |                  | Y20           |          |

**Notes: 1.** Not connected, leave pin open.

2. For internal use only, must be pulled low always.

**Remark:** All free pins are available for UDL.

### **Table of Contents**

|    |     | INT   | ERNAL BLOCK DIAGRAM                                     | <br>        | . 3  |

|----|-----|-------|---------------------------------------------------------|-------------|------|

|    |     | PIN   |                                                         | <br>        | . 4  |

|    |     | PIN   | CONFIGURATION                                           | <br>• • • • | . 5  |

| 1. |     |       | FUNCTIONS                                               |             |      |

|    | 1.1 |       | of Pin Functions                                        |             |      |

|    | 1.2 | Туре  | s of Pin I/O Circuit and Recommended Connection of Pins | <br>        | . 14 |

| 2. |     | ELE   | ECTRICAL SPECIFICATIONS                                 | <br>        | 16   |

|    | 2.1 | Abso  | lute Maximum Ratings                                    | <br>        | . 16 |

|    | 2.2 | Oper  | ating Conditions                                        | <br>        | . 16 |

|    | 2.3 | Oscil | llator Characteristics                                  | <br>        | . 17 |

|    | 2.4 | PLL ( | Characteristics                                         | <br>        | . 22 |

|    | 2.5 | DC C  | haracteristics                                          | <br>        | . 23 |

|    | 2.6 | AC C  | haracteristics                                          | <br>        | . 24 |

|    |     | 2.6.1 | General                                                 | <br>        | . 24 |

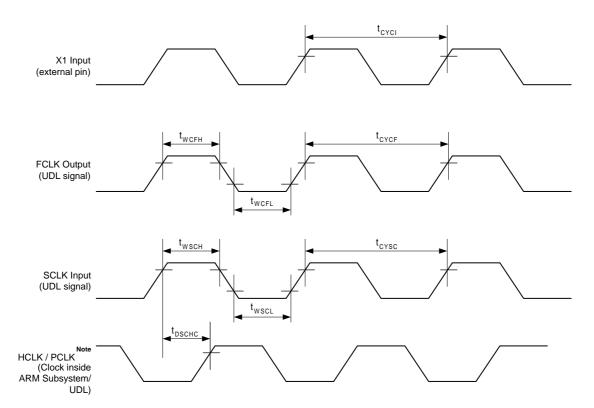

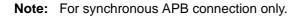

|    |     | 2.6.2 | Clock Timing                                            | <br>        | . 25 |

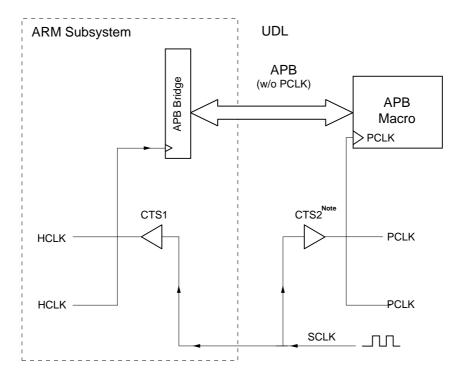

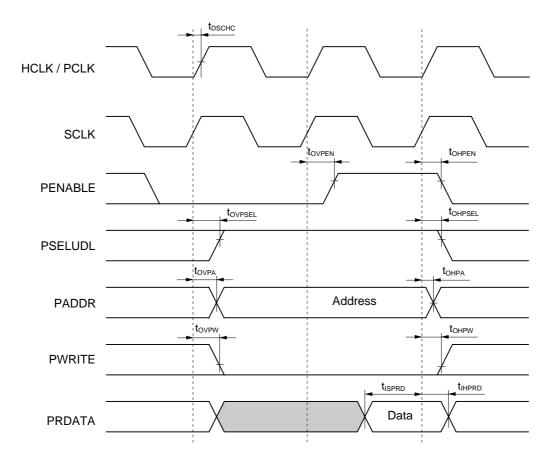

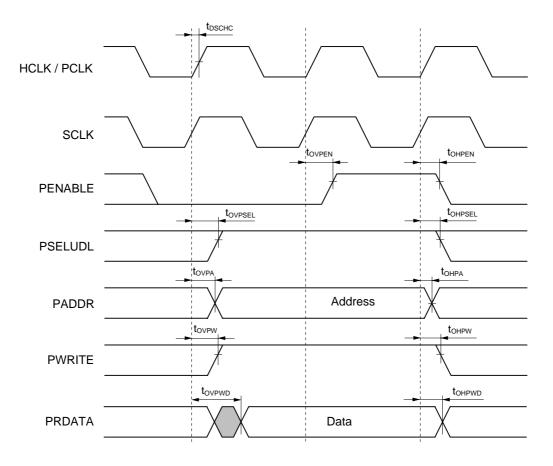

|    |     | 2.6.3 | APB Bus Timing                                          | <br>        | . 26 |

|    |     | 2.6.4 | External Memory Bus Timing                              |             |      |

|    |     | 2.6.5 | Reset Timing.                                           | <br>        | . 34 |

|    |     | 2.6.6 | Interrupt Timing                                        |             |      |

| 3. |     | PAG   | CKAGE DRAWING                                           | <br>        | 37   |

| 4. |     | REC   | COMMENDED SOLDERING CONDITIONS                          | <br>        | 38   |

### List of Figures

| Figure 2-1:  | Crystal or Ceramic Resonator Connection                          |    |

|--------------|------------------------------------------------------------------|----|

| Figure 2-2:  | External Clock Input                                             |    |

| Figure 2-3:  | Examples of Incorrect Resonator Connection (1/2)                 | 20 |

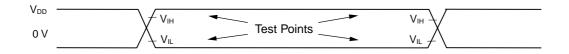

| Figure 2-4:  | AC Test Input Measurement Points (external signals)              | 24 |

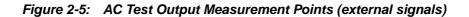

| Figure 2-5:  | AC Test Output Measurement Points (external signals)             | 24 |

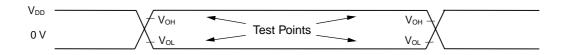

| Figure 2-6:  | AC Test Load Condition                                           | 24 |

| Figure 2-7:  | Clock Waveforms                                                  |    |

| Figure 2-8:  | Clock Structure                                                  |    |

| Figure 2-9:  | APB Read Cycle                                                   |    |

| Figure 2-10: | APB Write Cycle                                                  |    |

| Figure 2-11: | External Memory Bus Single Read Cycle                            | 30 |

| Figure 2-12: | External Memory Bus Sequential Read Cycle                        |    |

| Figure 2-13: | External Memory Bus Page Mode Read Cycle (32-bit wide)           |    |

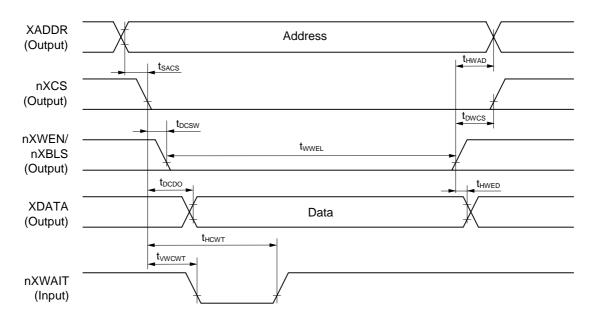

| Figure 2-14: | External Memory Bus Single Write Cycle                           | 32 |

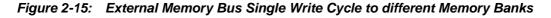

| Figure 2-15: | External Memory Bus Single Write Cycle to different Memory Banks | 32 |

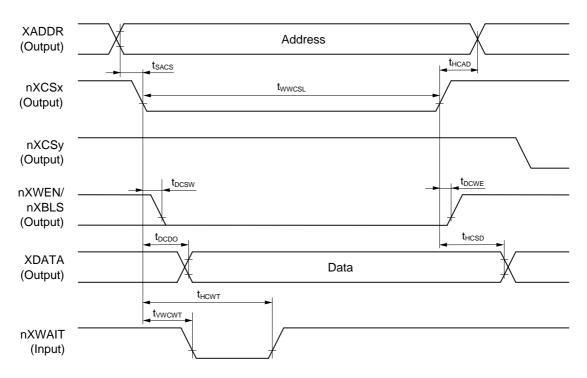

| Figure 2-16: | External Memory Bus Sequential Write Cycle                       | 33 |

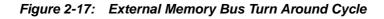

| Figure 2-17: | External Memory Bus Turn Around Cycle                            | 33 |

| Figure 2-18: | Reset Cycle                                                      |    |

| Figure 2-19: | Interrupt Cycle                                                  |    |

| Figure 3-1:  | Package Drawing                                                  |    |

|              |                                                                  |    |

### List of Tables

| Table 1-1:  | External Pins                                                                            | 11 |

|-------------|------------------------------------------------------------------------------------------|----|

| Table 1-2:  | Internal Pins between ARM subsystem and UDL                                              | 13 |

| Table 1-3:  | Types of Pin I/O Circuit and Recommended Connection of Pins                              | 14 |

| Table 2-1:  | Absolute Maximum Ratings                                                                 | 16 |

| Table 2-2:  | Operating Conditions                                                                     | 16 |

| Table 2-3:  | Oscillator Characteristics (TA = -40 to +85°C, VDD = 3.3 V ± 0.3 V)                      |    |

| Table 2-4:  | Oscillator Characteristics (TA = -40 to +85°C, VDD = 3.3 V ± 0.3 V)                      | 18 |

| Table 2-5:  | PLL Recommended Operating Range (TA = -40 to +85°C, AVDD = 3.3 V ± 0.3 V)                | 22 |

| Table 2-6:  | PLL Specification (TA = -40 to +85°C, AVDD = 3.3 V ± 0.3 V)                              | 22 |

| Table 2-7:  | DC Characteristics (TA = -40 to +85°C; VDD, DVDD, AVDD = $3.3 V \pm 0.3 V$ )             | 23 |

| Table 2-8:  | Conditions for AC Characteristics                                                        | 24 |

| Table 2-9:  | Clock AC Characteristics ( $T_A = -40$ to $+85^{\circ}$ C, $V_{DD} = 3.3$ V $\pm 0.3$ V) | 25 |

| Table 2-10: | APB Bus AC Characteristics (TA = -40 to $+85^{\circ}$ C, VDD = 3.3 V $\pm$ 0.3 V)        | 26 |

| Table 2-11: | External Memory Bus AC Characteristics (TA = -40 to +85°C, VDD = $3.3 V \pm 0.3 V$ ).    | 29 |

| Table 2-12: | Reset AC Characteristics (TA = -40 to +85°C, VDD = 3.3 V ± 0.3 V)                        | 34 |

| Table 2-13: | Interrupt AC Characteristics (TA = -40 to +85°C, VDD = 3.3 V ± 0.3 V)                    | 36 |

| Table 4-1:  | Soldering Conditions                                                                     | 38 |

|             |                                                                                          |    |

### 1. PIN FUNCTIONS

### 1.1 List of Pin Functions

### (1) External Pins

| Pin Name                    | I/O    | Function                                                                                       | Interface     |  |

|-----------------------------|--------|------------------------------------------------------------------------------------------------|---------------|--|

| nXOE                        | Output | Data output enable                                                                             |               |  |

| nXWEN                       | Output | Write enable signal output                                                                     |               |  |

| nXWAIT                      | Input  | Control signal input to insert wait in bus cycle                                               |               |  |

| nXBLS0                      |        |                                                                                                |               |  |

| nXBLS1                      | Output | Byte lane select signal output                                                                 |               |  |

| nXBLS2                      | Output | Byte lane select signal output                                                                 |               |  |

| nXBLS3                      |        |                                                                                                |               |  |

| nXCS0                       |        |                                                                                                |               |  |

| nXCS1                       |        |                                                                                                | External Bus  |  |

| nXCS2                       |        |                                                                                                | Interface     |  |

| nXCS3                       | Output | Chip select signal output                                                                      |               |  |

| nXCS4                       | Output |                                                                                                |               |  |

| nXCS5                       |        |                                                                                                |               |  |

| nXCS6                       |        |                                                                                                |               |  |

| nXCS7                       |        |                                                                                                |               |  |

| XADDR0 to<br>XADDR25 Output |        | 26-bit address bus for external memory                                                         |               |  |

| XDATA0 to<br>XDATA31        | I/O    | 32-bit data bus for external memory                                                            |               |  |

| RXD                         | Input  | Serial receive data input                                                                      | Serial        |  |

| TXD                         | Output | Serial transmit data output                                                                    | Interface     |  |

| X1                          | Input  | Connects the crystal resonator for system clock oscillation.                                   | Oscillator    |  |

| X2                          | -      | In the case of an external source supplying the clock, it is input to X2 (direct clock input). | Interface     |  |

| TCLK <sup>Note 1</sup>      | Input  | Clock input for test purpose                                                                   |               |  |

| nRST                        | Input  | System reset input                                                                             |               |  |

| EA0 <sup>Note 4</sup>       | Input  | Enable external best memory                                                                    |               |  |

| EA1 <sup>Note 4</sup>       | Input  | Enable external boot memory                                                                    | System        |  |

| DBGEN <sup>Note 4</sup>     | Input  | Debug enable input                                                                             | Configuration |  |

| PLLOD0 <sup>Note 4</sup>    | Input  | Frequency of PLL output clock (FCLK)                                                           | Interface     |  |

| PLLOD1 <sup>Note 4</sup>    | Input  |                                                                                                |               |  |

| IC1 <sup>Note 2</sup>       | -      | Internal connected                                                                             |               |  |

| TEST <sup>Note 3</sup>      | -      | Internal connection                                                                            |               |  |

### Table 1-1: External Pins (1/2)

| Pin Name                                    | I/O    | Function                                         | Interface           |

|---------------------------------------------|--------|--------------------------------------------------|---------------------|

| AV <sub>DD</sub>                            | Input  | Positive analog power supply for PLL             |                     |

| DV <sub>DD</sub>                            | Input  | Positive digital power supply for PLL            |                     |

| AV <sub>SS</sub>                            | Input  | Analog ground potential for PLL                  | Power               |

| DV <sub>SS</sub> Input                      |        | Digital ground potential for PLL                 | Supply<br>Interface |

| V <sub>DD0</sub> to V <sub>DD11</sub> Input |        | Positive power supply                            |                     |

| V <sub>SS0</sub> to V <sub>SS12</sub> Input |        | Ground potential                                 |                     |

| JTAG_TDI                                    | Input  | Data in for debugging or boundary scan           |                     |

| JTAG_TDO                                    | Output | Data out for debugging or boundary scan          | Debug and           |

| JTAG_TCK Input                              |        | Clock input for debugging or boundary scan       | Boundary Scan       |

| JTAG_TMS Input                              |        | Mode select input for debugging or boundary scan | Interface           |

| JTAG_TRST                                   | Input  | Reset input for debugging or boundary scan       |                     |

### Table 1-1: External Pins (2/2)

**Notes: 1.** Must be kept low in normal operating mode.

- 2. Not connected, leave pin open.

- 3. Must be pulled low always.

- 4. Must be kept unchanged during operation.

### (2) Internal Pins between ARM subsystem and UDL

| Pin Name               | Direction | Function                                  | Interface                  |

|------------------------|-----------|-------------------------------------------|----------------------------|

| PRESETn                | to UDL    | APB bus reset signal                      |                            |

| PSELUDL                | to UDL    | APB bus slave select signal               |                            |

| PENABLE                | to UDL    | APB bus strobe signal                     |                            |

| PWRITE                 | to UDL    | APB bus write signal                      |                            |

| PADDR0 to<br>PADDR28   | to UDL    | APB address bus                           | APB Bus<br>Interface       |

| PRDATA0 to<br>PRDATA31 | from UDL  | APB read data bus                         |                            |

| PWDATA0 to<br>PWDATA31 | to UDL    | APB write data bus                        | _                          |

| FCLK                   | to UDL    | PLL output frequency                      | Clock                      |

| SCLK                   | from UDL  | Clock for ARM subsystem                   | Interface                  |

| INT0 to INT28          | from UDL  | Interrupt lines to interrupt controller   |                            |

| nRESUDL                | from UDL  | Reset signal from UDL to reset controller | Interrupt/Exception        |

| nFIRQ                  | from UDL  | FIQ signal directly routed to ARM CPU     |                            |

| PLL_M0 to<br>PLL_M4    | from UDL  | M value for M-counter of PLL              | PLL                        |

| PLL_N0 to PLL_N6       | from UDL  | N value for N-counter of PLL              | Configuration              |

| PLL_S0 to PLL_S1       | from UDL  | VCO frequency range selection             |                            |

| TARMSS                 | from UDL  | Set ARM subsystem into test mode          |                            |

| BS_TCK                 |           |                                           |                            |

| BS_TMS                 | to UDL    | Boundary scan signals for UDL             | Boundary Scan<br>Interface |

| BS_TRST                |           |                                           |                            |

Table 1-2:

Internal Pins between ARM subsystem and UDL

### 1.2 Types of Pin I/O Circuit and Recommended Connection of Pins

| Pin               | I/O Buffer Type <sup>Note</sup> | Recommended Connection                                                                                            |  |  |

|-------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| nXOE              | D) (00                          |                                                                                                                   |  |  |

| nXWEN             | BV08                            | Output: Leave open (if unused)                                                                                    |  |  |

| nXWAIT            | FIV1                            | Input: Connect to V <sub>DD</sub> via a resistor (if unused)                                                      |  |  |

| nXBLS0            | D)/00                           |                                                                                                                   |  |  |

| nXBLS1            | BV08                            | Output: Leave open (if unused)                                                                                    |  |  |

| nXBLS2            | BW03                            | Output: Leave open (if unused)                                                                                    |  |  |

| nXBLS3            | Bw03                            |                                                                                                                   |  |  |

| nXCS0             |                                 |                                                                                                                   |  |  |

| nXCS1             |                                 |                                                                                                                   |  |  |

| nXCS2             |                                 |                                                                                                                   |  |  |

| nXCS3             |                                 |                                                                                                                   |  |  |

| nXCS4             | BV08                            | Output: Leave open (if unused)                                                                                    |  |  |

| nXCS5             |                                 |                                                                                                                   |  |  |

| nXCS6             |                                 |                                                                                                                   |  |  |

| nXCS7             |                                 |                                                                                                                   |  |  |

| XADDR0 to XADDR25 |                                 |                                                                                                                   |  |  |

| XDATA0 to XDATA31 | BW03                            | Input: Connect to V <sub>DD</sub> or V <sub>SS</sub> via a resistor (if unused)<br>Output: Leave open (if unused) |  |  |

| RXD               | FIV1                            | Input: Connect to $V_{DD}$ or $V_{SS}$ via a resistor (if unused)                                                 |  |  |

| TXD               | BV08                            | Output: Leave open (if unused)                                                                                    |  |  |

| X1                | OSI1 / OSO1                     | Connect to $V_{SS}$ (when external clock is input to X2 pin)                                                      |  |  |

| X2                | 031170301                       |                                                                                                                   |  |  |

| TCLK              | FIV1                            | Must be kept low in normal operation mode                                                                         |  |  |

| nRST              | FIF1                            | Schmitt-Trigger input                                                                                             |  |  |

| EA0               | FIV1                            | Must be set to an appropriate value to guarantee                                                                  |  |  |

| EA1               |                                 | correct operation                                                                                                 |  |  |

| DBGEN             | FDV1                            | internal pull-down (50K)                                                                                          |  |  |

| PLLOD0            |                                 | Must be set to an appropriate value to guarantee                                                                  |  |  |

| PLLOD1            | FIV1                            | correct operation                                                                                                 |  |  |

| JTAG_TDI          |                                 | Connect to V <sub>DD</sub> (pull-up)                                                                              |  |  |

| JTAG_TDO          | BV08                            |                                                                                                                   |  |  |

| JTAG_TCK          |                                 |                                                                                                                   |  |  |

| JTAG_TMS          | FIV1                            | Connect to V <sub>DD</sub> (pull-up)                                                                              |  |  |

| JTAG_TRST         |                                 |                                                                                                                   |  |  |

| AV <sub>DD</sub>  | -                               | Default power supply (analog) for PLL                                                                             |  |  |

| DV <sub>DD</sub>  | -                               | Default power supply (digital) for PLL                                                                            |  |  |

| AV <sub>SS</sub>  | -                               | Default ground (analog) for PLL                                                                                   |  |  |

Table 1-3:

Types of Pin I/O Circuit and Recommended Connection of Pins (1/2)

| Table 1-3: | Types of Pin I/O Circuit and Recommended Connection of Pins (2/2) |

|------------|-------------------------------------------------------------------|

|------------|-------------------------------------------------------------------|

| Pin                                   | I/O Buffer Type <sup>Note</sup> | Recommended Connection           |

|---------------------------------------|---------------------------------|----------------------------------|

| DV <sub>SS</sub>                      | -                               | Default ground (digital) for PLL |

| V <sub>DD0</sub> to V <sub>DD11</sub> | -                               | Default power supply             |

| $\rm V_{SS0}$ to $\rm V_{SS12}$       | -                               | Default ground                   |

**Note:** For buffer type information, please refer to document "Block Library CMOS-9HD Family, EA-9HD Family" (Document No. A13052EJ6V0BL00).

### 2. ELECTRICAL SPECIFICATIONS

### 2.1 Absolute Maximum Ratings

| Parar             | neter       | Symbol                           | Test Conditions                          | Ratings     | Unit |

|-------------------|-------------|----------------------------------|------------------------------------------|-------------|------|

| Supply voltage    |             | $V_{DD}$ , $DV_{DD}$ , $AV_{DD}$ |                                          | -0.5 ~ +4.6 | V    |

| Input voltage     | except X1   | VI                               | $V_{\rm I} < V_{\rm DD} + 3.0 \ {\rm V}$ | -0.5 ~ +6.6 | V    |

| Output voltage    | except X2   | V <sub>O</sub>                   | $V_{O} < V_{DD} + 3.0 V$                 | -0.5 ~ +6.6 | V    |

| Output current    | except X2   | Ι <sub>Ο</sub>                   |                                          | 30          | mA   |

| Operating ambient | temperature | T <sub>A</sub>                   |                                          | -40 ~ +85   | °C   |

| Storage temperatu | re          | T <sub>STG</sub>                 |                                          | -65 ~ +150  | °C   |

| Table 2-1: | Absolute Maximu | m Ratings |

|------------|-----------------|-----------|

|            |                 | in naings |

- Cautions: 1. Do not directly connect output (or I/O) pins of IC products to each other, or to  $V_{DD}$ ,  $V_{CC}$ , and GND. Open drain pins or open collector pins, however, can be directly connected to each other. Direct connection of the output pins between an IC product and an external circuit is possible, if the output pins can be set to the high-impedance state and the output timing of the external circuit is designed to avoid output conflict.

- 2. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded. The ratings and conditions shown below for DC characteristics and AC characteristics are within the range for normal operation and quality assurance.

### 2.2 Operating Conditions

| Clock Input                                                        | Operating Ambient<br>Temperature (T <sub>A</sub> ) | Supply Voltage<br>(V <sub>DD</sub> ) | Operation Clock Frequency                       |  |

|--------------------------------------------------------------------|----------------------------------------------------|--------------------------------------|-------------------------------------------------|--|

| Oscillator Input<br>(crystal frequency<br>range) <sup>Note 2</sup> | -40 ~ +85°C                                        | 3.0 V ~ 3.6 V                        | 4 MHz $\leq$ f <sub>Crystal</sub> $\leq$ 16 MHz |  |

| ARM Subsystem Input<br>(SCLK frequency range)                      |                                                    |                                      | f <sub>SCLK</sub> ≤ 35 MHz <sup>Note 1</sup>    |  |

Table 2-2: Operating Conditions

**Notes: 1.** ARM subsystem operating frequency, as derived from PLL output clock (FCLK).

2. Input frequency for oscillator at external pins X1 and X2 or external pin X2, if a direct clock source is used.

### 2.3 Oscillator Characteristics

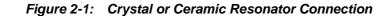

(a) Crystal or Ceramic Resonator Connection

Table 2-3: Oscillator Characteristics ( $T_A = -40$  to  $+85^{\circ}$ C,  $V_{DD} = 3.3$  V  $\pm 0.3$  V)

| Parameter                      | Symbol           | Conditions                | MIN. | TYP. | MAX. | Unit |

|--------------------------------|------------------|---------------------------|------|------|------|------|

| Oscillation frequency          | fxx              | $V_{DD}$ = 3.0 V to 3.6 V | 4    |      | 16   | MHz  |

| Oscillation stabilization time | t <sub>OST</sub> |                           |      | 10   |      | ms   |

**Note:** The value of the oscillation stabilization time is just a typical value. It greatly depends on the application (external components, PCB layout).

### Caution: Ensure that the duty cycle of oscillation waveform is between 45% and 55%.

**Remark:** PCB layout recommendations are listed in sub-chapter (c).

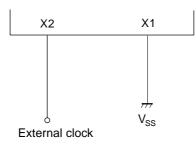

### (b) External Clock Input

The external clock shall be connected to the X2 output while clamping X1 to ground (V<sub>SS</sub>).

| Parameter       | Symbol | Conditions                | MIN. | TYP. | MAX. | Unit |

|-----------------|--------|---------------------------|------|------|------|------|

| Input frequency | fxx    | $V_{DD}$ = 3.0 V to 3.6 V | 4    |      | 16   | MHz  |

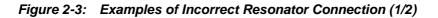

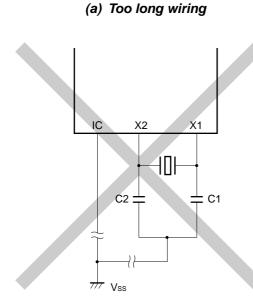

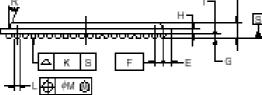

### (c) PCB layout recommendations for crystal oscillator wiring

Since crystal oscillators are very EMI sensitive, it is strongly recommended to design the PCB board for the oscillator part very carefully according to the below listed recommendations.

The oscillator consists of an inverter inside SOClite ASIC that is connected to a quartz-crystal. The inverter is bridged by an internal feedback resistor. The inverter within SOClite ASIC has a high input impedance (X1 pin) and high output impedance (X2 pin). The output pin X2 has a low drive capability in order not to overdrive or damage the crystal. Internally, the oscillator signal is fed via a buffer chain to a 2:1 pre-scaler inside the PLL. The pre-scaler divides the oscillator input by two, which ensures a stable 50% duty cycle clock as PLL input signal.

In case of a poor PCB layout, noise injection into the on-chip oscillator may cause unintended noise spikes at the output of the internal oscillator buffer stage. The spiky signal will be divided by two and then further be filtered by the PLL characteristics. In case of an injected noise spike, a slowly decaying frequency disturbance at the PLL output would be observable.

The PCB layout recommendations for the oscillator part are as follows:

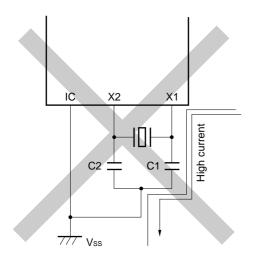

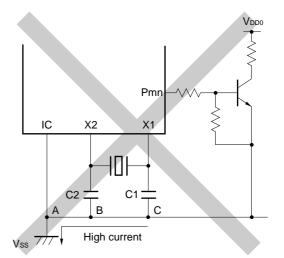

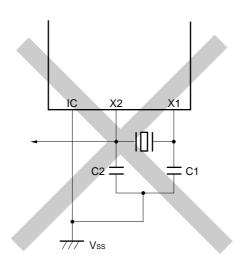

- Ground path distance between the capacitors C1 and C2 and the ground pin V<sub>SS10</sub> should be as short as possible.

- The oscillator must not share its ground trace with other signals (please refer to Figure 2-3 d).

- Place the crystal resonator and the capacitors C1 and C2 as close as possible to the X1 and X2 pins.

- Keep the wiring lengths as short as possible.

- Ensure that no other signals cross or/and accompany the crystal wiring (please refer to Figure 2-3 b/c).

- Enclose the oscillator circuitry with a ground guard ring as much as possible. Even a very thin guard ring due to PCB routing restrictions, is much better than having no guard ring at all.

- Apply an as complete as possible ground shielding to X1 and X2 oscillator signals. Shielding tracks on both sides of X1 and X2 oscillator signals must be connected to the ground plane at both ends and at least every 5 to 10 mm. Further, a local ground plane on the adjacent layers may be required.

- Keep any fast switching and/or high fluctuating current flows away from the oscillator lines.

- Do not fetch signals directly from the oscillator (please refer to Figure 2-3 e)

- Choose the capacitance C2 attached to X2 pin as big as possible. A value of at least 68 pF is strongly recommended. It may be necessary to use a dedicated crystal for achieving the target center oscillation frequency. Please contact your crystal vendor for that purpose for further details.

- As starting value, C1 should be chosen equal to C2. It must be ensured by appropriate measurements that the X1 input signal does not exceed the maximum ratings. The input level can be decreased, by increasing C1 appropriately.

- Do not insert a series resistor Rs in your final PCB-layout.

NEC strongly recommends to prove the effectiveness of these measures after E/S silicon availability in an early stage of the project.

If your system is sensitive to sporadic frequency disturbances due to injected noise, we recommend to use an external crystal oscillator instead, that is hooked up to the X2 output pin, while X1 input clamped to GND (see Figure 2-2). Keep the wiring between external oscillator and X2 pin short.

(b) Crossed signal line

(c) Wiring near high alternating current

(d) Current flowing through ground line of oscillator (potential at points A, B and C fluctuates)

(d) Signals are fetched

### 2.4 PLL Characteristics

| Parameter           | Symbol           | Conditions                           | MIN. | TYP. | MAX. | Unit |

|---------------------|------------------|--------------------------------------|------|------|------|------|

| Supply voltage      | AV <sub>DD</sub> |                                      | 3.0  | 3.3  | 3.6  | V    |

| PLL input frequency | f <sub>STD</sub> |                                      | 4    |      | 160  | MHz  |

| Divided ratio       | m                |                                      | 2    |      | 32   |      |

|                     | n                | Multiplication rate<br>= n / (m x p) | 2    |      | 128  |      |

|                     | р                | ··· , (···· F )                      | 2    |      | 8    |      |

### Table 2-5: PLL Recommended Operating Range ( $T_A = -40$ to $+85^{\circ}C$ , $AV_{DD} = 3.3$ V $\pm 0.3$ V)

Table 2-6: PLL Specification ( $T_A = -40$  to  $+85^{\circ}C$ ,  $AV_{DD} = 3.3 V \pm 0.3 V$ )

| Parameter               | Symbol            | Conditions                                      | MIN. | TYP. | MAX. | Unit |

|-------------------------|-------------------|-------------------------------------------------|------|------|------|------|

| Supply current          | I <sub>ADD</sub>  |                                                 |      |      | 20   | mA   |

| VCO output frequency    | f <sub>VCO</sub>  | frequency range set by<br>parameters PLL_S[1:0] | 50   |      | 230  | MHz  |

| PLL output clock        | f <sub>FCLK</sub> | set by parameters<br>PLLOD[1:0]                 | 6.25 |      | 115  | MHz  |

| PLL output ratio        | duty              | p = 2,4 or 8                                    | 45   |      | 55   | %    |

| Output period jitter    | t <sub>pj</sub>   | peak to peak                                    |      |      | 0.4  | ns   |

| Output long term jitter | t <sub>lj</sub>   | peak to peak                                    |      |      | 2.0  | ns   |

| PLL lock time           | tLock             |                                                 |      |      | 1    | ms   |

### 2.5 DC Characteristics

| Parameter                                       |                                   | Symbol           | Conditions                                 | MIN.                  | TYP. | MAX.            | Unit |

|-------------------------------------------------|-----------------------------------|------------------|--------------------------------------------|-----------------------|------|-----------------|------|

| High-level input voltage                        | all except:<br>nRST, X1           | V <sub>IH</sub>  |                                            | 2.0                   |      | 5.5             | V    |

| Low-level input voltage                         | all except:<br>nRST, X1           | V <sub>IL</sub>  |                                            | 0.0                   |      | 0.8             | V    |

| High-level input voltage                        | X1                                | V <sub>IHX</sub> |                                            | 2.0                   |      | V <sub>DD</sub> | V    |

| Low-level input voltage                         | X1                                | $V_{ILX}$        |                                            | 0                     |      | 0.8             | V    |

| Positive trigger voltage                        | nRST                              | V <sub>P</sub>   |                                            | 1.4                   |      | 2.4             | V    |

| Negative trigger voltage                        | nRST                              | V <sub>N</sub>   |                                            | 0.8                   |      | 1.6             | V    |

| Hysteresis voltage                              | nRST                              | V <sub>H</sub>   |                                            | 0.3                   |      | 1.5             | V    |

| Low-level output voltage                        |                                   | V <sub>OL</sub>  | I <sub>OL</sub> = 0 mA                     |                       |      | 0.1             | V    |

| High-level output voltage                       |                                   | V <sub>OH</sub>  | I <sub>OH</sub> = 0 mA                     | V <sub>DD</sub> - 0.2 |      |                 | V    |

| Static current consumption                      |                                   | I <sub>DDS</sub> | V <sub>I</sub> = V <sub>DD</sub> or<br>GND |                       | tbd  | tbd             | μA   |

| OFF-state<br>output current                     |                                   | I <sub>OZ</sub>  | V <sub>O</sub> = V <sub>DD</sub> or<br>GND |                       |      | ± 10            | μA   |

| Output short-circuit<br>current Note 1          |                                   | I <sub>OS</sub>  | $V_{O} = GND$                              |                       |      | - 250           | mA   |

| Input leakage current                           | all except:<br>TEST,<br>DBGEN, X1 | I <sub>LI1</sub> | V <sub>I</sub> = V <sub>DD</sub> or<br>GND |                       |      | ± 1             | μA   |

|                                                 | TEST,<br>DBGEN                    | I <sub>LI2</sub> | $V_{I} = V_{DD}$                           | 28                    | 83   | 190             | μA   |

| Pull-down resistor<br>(50 KΩ) <sup>Note 2</sup> | TEST,<br>DBGEN                    | R <sub>PD</sub>  | $V_{I} = V_{DD}$                           | 18.9                  | 39.8 | 107.1           | KΩ   |

| Low-level output current                        |                                   | I <sub>OL</sub>  | $V_{OL} = 0.4 V$                           | 9.0                   |      |                 | mA   |

| High-level output current                       |                                   | I <sub>OH</sub>  | V <sub>OH</sub> = 2.4 V                    | - 3.0                 |      |                 | mA   |

Notes: 1. The output short circuit time is 1 second or less per pin of SoCLite.

2. The pull-down resistance varies depending on the input and output voltage.

### 2.6 AC Characteristics

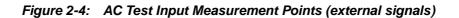

### 2.6.1 General

| Table 2-8: | Conditions | for AC | Characteristics |

|------------|------------|--------|-----------------|

|------------|------------|--------|-----------------|

|                                | UDL Signals                                                              | External Signals (Pins) |  |  |

|--------------------------------|--------------------------------------------------------------------------|-------------------------|--|--|

| Ambient temperature            | T <sub>A</sub> = -40 to +85°C                                            |                         |  |  |

| Operating voltage              | $V_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{ V}_{SS} = 0 \text{ V}$ |                         |  |  |

| Input signal rise/fall time    | ideal (= 0 ns)                                                           |                         |  |  |

| Output signal load capacitance | C <sub>L</sub> = 1 pF                                                    | C <sub>L</sub> = 50 pF  |  |  |

Figure 2-6: AC Test Load Condition

Caution: If the load capacitance of external signals (pins) exceeds 50 pF due to the circuit configuration, bring the load capacitance of the device to 50 pF or less by inserting a buffer or by some other means.

### 2.6.2 Clock Timing

NEC

| Parameter                    | Symbol             | Conditions | MIN. | MAX.  | Unit |

|------------------------------|--------------------|------------|------|-------|------|

| X1 input cycle               | t <sub>CYCI</sub>  |            | 62.5 | 250   | ns   |

| SCLK input cycle             | t <sub>CYSC</sub>  |            | 28.6 |       | ns   |

| SCLK input high-level width  | t <sub>WSCH</sub>  |            | 12.9 |       | ns   |

| SCLK input low-level width   | t <sub>WSCL</sub>  |            | 12.9 |       | ns   |

| SCLK to PCLK/HCLK delay Note | t <sub>DSCHC</sub> |            | 4.15 | 10.69 | ns   |

| FCLK output cycle            | t <sub>CYCF</sub>  |            | 8.7  | 160   | ns   |

| FCLK output high-level width | t <sub>WFIH</sub>  |            | 3.9  | 88    | ns   |

| FCLK output low-level width  | t <sub>WCFL</sub>  |            | 3.9  | 88    | ns   |

Table 2-9: Clock AC Characteristics ( $T_A = -40$  to  $+85^{\circ}C$ ,  $V_{DD} = 3.3$  V  $\pm$  0.3 V)

Note: For synchronous APB connection only.

### 2.6.3 APB Bus Timing

Figure 2-8: Clock Structure

**Note:** For synchronous operation of APB bus, adjust CTS2 (SCLK to PCLK delay) to CTS1 (SCLK to HCLK delay).

| Table 2-10: | APB Bus AC Characteristics | $(T_A = -40 \ tc)$ | • +85°C, V <sub>DD</sub> = | = 3.3 V ± 0.3 V) |

|-------------|----------------------------|--------------------|----------------------------|------------------|

|-------------|----------------------------|--------------------|----------------------------|------------------|

| Parameter                        | Symbol              | related to H | ICLK/PCLK | related to SCLK |      | Unit |

|----------------------------------|---------------------|--------------|-----------|-----------------|------|------|

| i arameter                       | Symbol              | MIN.         | MAX.      | MIN.            | MAX. | Onit |

| PENABLE valid after rising clock | t <sub>OVPEN</sub>  |              | 2.9       |                 | 13.5 | ns   |

| PENABLE hold after rising clock  | t <sub>OHPEN</sub>  | 0.9          |           | 5.1             |      | ns   |

| PSELUDL valid after rising clock | t <sub>OVPSEL</sub> |              | 2.7       |                 | 13.4 | ns   |

| PSELUDL hold after rising clock  | t <sub>OHPSEL</sub> | 0.9          |           | 5.0             |      | ns   |

| PADDR valid after rising clock   | t <sub>OVPA</sub>   |              | 3.3       |                 | 14.0 | ns   |

| PADDR hold after rising clock    | t <sub>OHPA</sub>   | 0.6          |           | 4.8             |      | ns   |

| PWRITE valid after rising clock  | t <sub>OVPW</sub>   |              | 2.9       |                 | 13.6 | ns   |

| PWRITE hold after rising clock   | t <sub>OHPW</sub>   | 1.0          |           | 5.1             |      | ns   |

| PRDATA setup to rising clock     | t <sub>ISPRD</sub>  | 16.7         |           | 8.2             |      | ns   |

| PRDATA hold after rising clock   | t <sub>IHPRD</sub>  | 0            |           | 0               |      | ns   |

| PWDATA valid after rising clock  | t <sub>OVPWD</sub>  |              | 4.6       |                 | 15.3 | ns   |

| PWDATA hold after rising clock   | t <sub>OHPWD</sub>  | 1.0          |           | 5.2             |      | ns   |

**Remark:** If the APB bus is connected synchronously to the ARM subsystem use the min. and max. values related to HCLK/PCLK, if it is connected asynchronously use the min. and max. values related to SCLK.

**Remark:** If the APB bus is connected synchronously to the ARM subsystem use the min. and max. values related to HCLK/PCLK, if it is connected asynchronously use the min. and max. values related to SCLK.

**Remark:** If the APB bus is connected synchronously to the ARM subsystem use the min. and max. values related to HCLK/PCLK, if it is connected asynchronously use the min. and max. values related to SCLK.

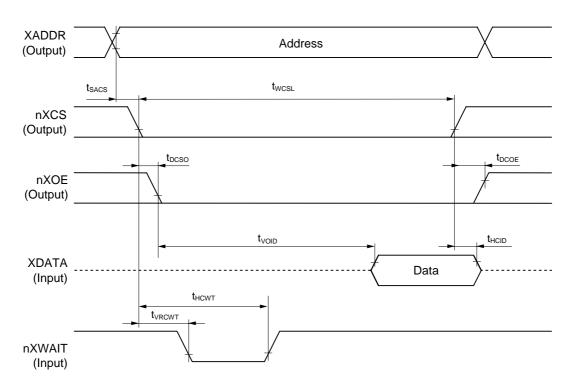

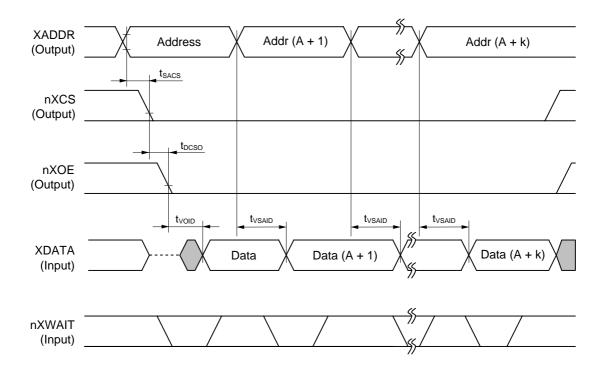

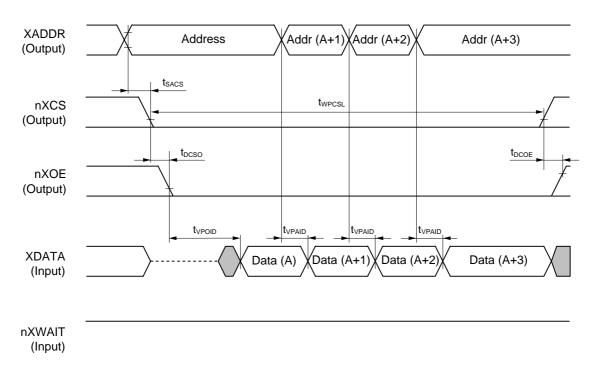

### 2.6.4 External Memory Bus Timing

|       | Parameter                                                                | Symbol             | Conditions | MIN.                                    | MAX.                      | Unit |

|-------|--------------------------------------------------------------------------|--------------------|------------|-----------------------------------------|---------------------------|------|

|       | Address setup time before nXCS $\downarrow$                              | t <sub>SACS</sub>  |            | T - 1.6                                 |                           | ns   |

|       | Delay time from nXCS $\downarrow$ to nXOE $\downarrow$                   | t <sub>DCSO</sub>  |            |                                         | 5.9                       | ns   |

|       | nXCS low level width (single read)                                       | t <sub>WCSL</sub>  |            | (WST1 + n + 3) T<br>- 1.2               |                           | ns   |

|       | nXCS low level width (page mode)<br>Note 3                               | t <sub>WPCSL</sub> |            | (WST1 + 2)T +<br>(3 WST2 + 7)T -<br>1.2 |                           | ns   |

| Read  | Data input valid after nXOE $\downarrow$ (single read)                   | t <sub>VOID</sub>  |            |                                         | (WST1 + n + 2)T -<br>22.8 | ns   |

|       | Data input valid after nXOE↓ (page mode) <sup>Note 3</sup>               | t <sub>VPOID</sub> |            |                                         | (WST1 + 2)T<br>- 22.8     | ns   |

|       | Data input valid after address (inside page) <sup>Note 3</sup>           | t <sub>VPAID</sub> |            |                                         | (WST2 + 1)T<br>- 18.6     | ns   |

|       | Data input hold time (from nXCS↑)                                        | t <sub>HCID</sub>  |            | 0                                       |                           | ns   |

|       | Delay time from nXCS↑ to nXOE↑                                           | t <sub>DCOE</sub>  |            |                                         | 6.2                       | ns   |

|       | Data input valid after address<br>(sequential read)                      | t <sub>VSAID</sub> |            |                                         | (WST1 + n + 2)T -<br>18.6 | ns   |

|       | nXWAIT valid after chip select (read)                                    | t <sub>VRCWT</sub> |            |                                         | (WST1 - 1)T<br>- 13.0     | ns   |

| Wait  | nXWAIT hold time (from chip select)                                      | t <sub>HCWT</sub>  |            | n x T                                   |                           | ns   |

|       | nXWAIT valid after chip select (write)                                   | t <sub>VWCWT</sub> |            |                                         | (WST2 - 2)T<br>- 13.0     | ns   |

|       | Delay time from nXCS↓ to nXWEN↓ /<br>nXBLS↓                              | t <sub>DCSW</sub>  |            |                                         | 7.5                       | ns   |

|       | nXWEN / nXBLS low level width                                            | t <sub>WWEL</sub>  |            | (WST2 + n + 1)T -<br>0.7                |                           | ns   |

|       | Delay time from nXWEN↑ / nXBLS↑ to<br>nXCS↑ <sup>Note 1</sup>            | t <sub>DWCS</sub>  |            | T - 7.3                                 |                           | ns   |

|       | Delay time from nXCS↓ to<br>data output                                  | t <sub>DCDO</sub>  |            |                                         | 5.7                       | ns   |

| Write | Data output hold time (from nXWEN↑<br>/ nXBLS↑) Note 1                   | t <sub>HWED</sub>  |            | T - 9.6                                 |                           | ns   |

| vine  | nXCS low level width Note 2                                              | t <sub>WWCSL</sub> |            | (WST2 + n + 1)T -<br>1.2                |                           | ns   |

|       | Delay time from nXCS↑ to nXWEN↑ /<br>nXBLS↑ <sup>Note 2</sup>            | t <sub>DCWE</sub>  |            | 1.6                                     |                           | ns   |

|       | Data output hold time (from nXCS <sup>↑</sup> )<br>Note 2                | t <sub>HCSD</sub>  |            | 2T - 4.0                                |                           | ns   |

|       | Delay time from nXWEN↓ / nXBLS↓<br>to next nXWEN↓ / nXBLS↓               | t <sub>DSWE</sub>  |            | (WST2 + n + 3)T                         |                           | ns   |

|       | Address hold time (from nXWEN <sup>↑</sup> / nXBLS <sup>↑</sup> ) Note 1 | t <sub>HWAD</sub>  |            | T - 8.6                                 |                           | ns   |

### Table 2-11: External Memory Bus AC Characteristics ( $T_A = -40$ to $+85^{\circ}$ C, $V_{DD} = 3.3$ V $\pm$ 0.3 V) (1/2)

### Table 2-11: External Memory Bus AC Characteristics ( $T_A = -40$ to +85°C, $V_{DD} = 3.3$ V ± 0.3 V) (2/2)

|        | Parameter                                                       | Symbol             | Conditions | MIN.                 | MAX. | Unit |

|--------|-----------------------------------------------------------------|--------------------|------------|----------------------|------|------|

| Write  | Address hold time (from nXCS <sup>↑</sup> ) <sup>Note 2</sup>   | t <sub>HCAD</sub>  |            | T - 5.2              |      | ns   |

| Turn   | nXCS high level width (turn around inside the same memory bank) | t <sub>WCSH1</sub> |            | (IDCY + 1)T<br>- 1.2 |      | ns   |

| Around | nXCS high level width (turn around to a different memory bank)  | t <sub>WCSH2</sub> |            | (IDCY + 1)T<br>- 4.1 |      | ns   |

Notes: 1. Write access inside the same memory bank.

- 2. Consecutive write access to a different memory bank.

- **3.** It is assumed that nXWAIT input is kept HIGH during page mode. Therefore n is not considered in the equation.

Remarks: 1. T : Clock period of SCLK.

- 2. WST1 : Content of WST1 inside the appropriate SMCBCRx register, (WST1 shall be greater than value 2).

- **3.** WST2 : Content of WST2 inside the appropriate SMCBCRx register, (WST2 shall be greater than value 3).

- 4. n : Number of wait states inserted into the bus cycle by nXWAIT input.

### Figure 2-11: External Memory Bus Single Read Cycle

Figure 2-12: External Memory Bus Sequential Read Cycle

Figure 2-13: External Memory Bus Page Mode Read Cycle (32-bit wide)

Figure 2-14: External Memory Bus Single Write Cycle

Figure 2-16: External Memory Bus Sequential Write Cycle

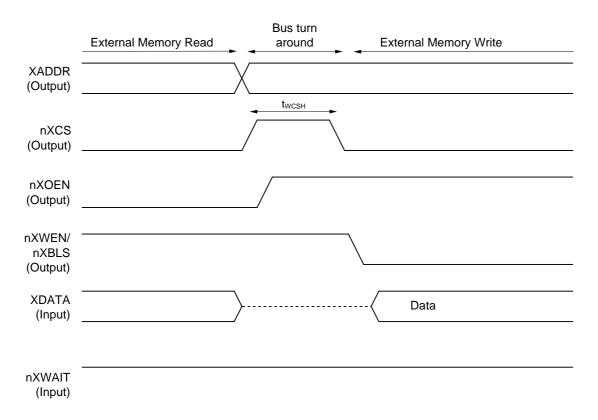

### 2.6.5 Reset Timing

| Parameter                                  | Symbol             | Conditions | MIN.                    | MAX.                               | Unit |

|--------------------------------------------|--------------------|------------|-------------------------|------------------------------------|------|

| nRST low-level width                       | t <sub>WRSL</sub>  |            | 2 T <sub>OSC</sub> + 70 |                                    | ns   |

| nRESUDL low-level width                    | t <sub>WRUL</sub>  |            | 2 T <sub>SCLK</sub>     |                                    | ns   |

| nRST hold time from V <sub>DD</sub>        | t <sub>HVRSL</sub> |            | 2 T <sub>OST</sub> + 1  |                                    | μs   |

| PRESETn delay from nRST falling edge       | t <sub>LRSPD</sub> |            |                         | 2 T <sub>OSC</sub> + 70            | ns   |

| PRESETn delay from nRST rising edge        | t <sub>HRSPD</sub> |            |                         | 2 <sup>14</sup> x T <sub>OSC</sub> | ns   |

| PRESETn delay from nRESUDL falling<br>edge | t <sub>LRUPD</sub> |            |                         | 4 T <sub>SCLK</sub>                | ns   |

| PRESETn delay from nRESUDL rising<br>edge  | t <sub>HRUPD</sub> |            |                         | 7 T <sub>SCLK</sub>                | ns   |

### Table 2-12: Reset AC Characteristics ( $T_A = -40$ to $+85^{\circ}C$ , $V_{DD} = 3.3$ V $\pm 0.3$ V)

**Remarks: 1.**  $T_{SCLK}$  : Clock period of SCLK.

**2.**  $T_{OSC}$  : Clock period of oscillator.

3.  $T_{OST}$  : Oscillation stabilization time.

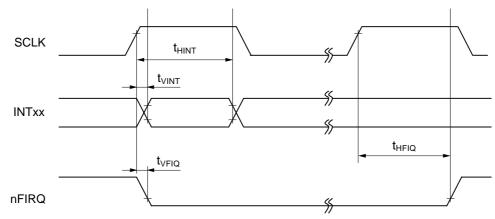

### 2.6.6 Interrupt Timing

| Table 2-13: | Interrupt AC Characteristics ( $T_A = -40$ to +85°C, $V_{DD} = 3.3$ V $\pm 0.3$ V) |

|-------------|------------------------------------------------------------------------------------|

|-------------|------------------------------------------------------------------------------------|

| Parameter                                   | Symbol            | Conditions | MIN. | MAX. | Unit |

|---------------------------------------------|-------------------|------------|------|------|------|

| INTxx input valid after rising edge of SCLK | t <sub>VINT</sub> |            |      | 2.5  | ns   |

| INTxx input hold time                       | t <sub>HINT</sub> |            | 10.4 |      | ns   |

| nFIRQ input valid after rising edge of SCLK | t <sub>VFIQ</sub> |            |      | 3.1  | ns   |

| nFIRQ input hold time                       | t <sub>HFIQ</sub> |            | 9.0  |      | ns   |

**Remark:** The min. and max. values are related to SCLK.

Figure 2-19: Interrupt Cycle

nFIRQ should be active until exception handler is executed

### 3. PACKAGE DRAWING

### 256-PIN PLASTIC BGA (27x27)

#### NOTE

Each ball centerline is located within  $\phi$ 0.3 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLINETERS      |

|------|------------------|

| A    | 27.0±0.2         |

| B    | 24.0             |

| 0    | 24.0             |

| D    | $27.0\pm0.2$     |

| E    | 1.44             |

| F    | 1.27 (T.P.)      |

| G    | 0.6±0.1          |

| н    | 0.36             |

| 1    | 1.5310.15        |

| J.   | 2.1310.25        |

| К    | 0.15             |

| L.   | \$0.75±0.15      |

| М    | 0.3              |

| P    | C3.95            |

| R    | 30°              |

| 5    | 1.5              |

|      | \$25651-127-06-2 |

and a second of the second second

### 4. RECOMMENDED SOLDERING CONDITIONS

Solder this product under the following recommended conditions.

For details of the recommended soldering conditions, refer to information document **Semiconductor Device Mounting Technology Manual (C10535E).**

For soldering methods and conditions other than those recommended, consult NEC.

| Soldering Method | Soldering Condition                                                                                                                                                                                 | Symbol Code of Recommended<br>Soldering Condition |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| Infrared reflow  | Package peak temperature: 230°C<br>Time of temperature higher than 210°C:<br>30 seconds max.<br>Number of reflows: 3 max.<br>Number of storage days after opening of dry<br>pack: 3 Note            | IR30-203-3                                        |  |

| VPS              | Package peak temperature: 215°C<br>Time of temperature higher than 200°C:<br>40 seconds max.<br>Number of reflows: 3 max.<br>Number of storage days after opening of dry<br>pack: 3 <sup>Note</sup> | VP15-203-3                                        |  |

Table 4-1:

Soldering Conditions

**Note:** The number of days refers to storage at 25°C, 65% RH MAX after the dry pack has been opened. After that, prebaking is necessary at 125°C for 20 hours (min.), 72 hours (max.).

## Caution: Do not use two or more soldering methods in combination (except partial heating method).

### NOTES FOR CMOS DEVICES -

### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

### **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics Inc. (U.S.)

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC Electronics (Europe) GmbH

Duesseldorf, GermanyTel:0211-65 03 01Fax:0211-65 03 327

#### Sucursal en España

Madrid, Spain Tel: 091- 504 27 87 Fax: 091- 504 28 60

#### Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99 Filiale Italiana Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

**Branch The Netherlands** Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

#### **Branch Sweden**

Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290 NEC Electronics Hong Kong Ltd.

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

### NEC Electronics Singapore Pte. Ltd.

Singapore Tel: 65-253-8311 Fax: 65-250-3583

NEC Electronics Taiwan Ltd.